Part Number: LP-AM263P

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,

I have a couple questions about creating GPIO input interrupts.

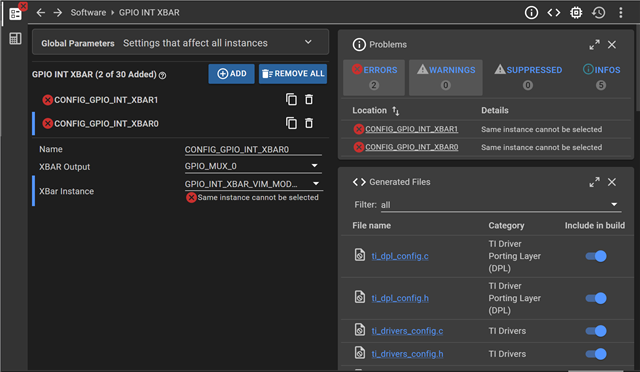

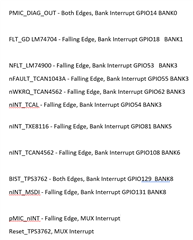

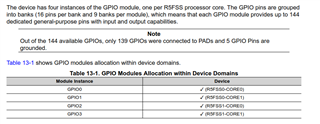

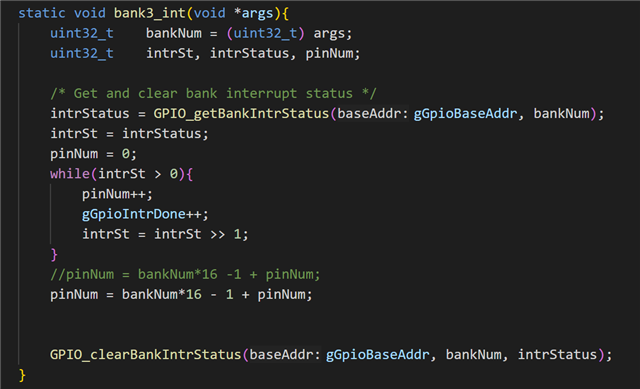

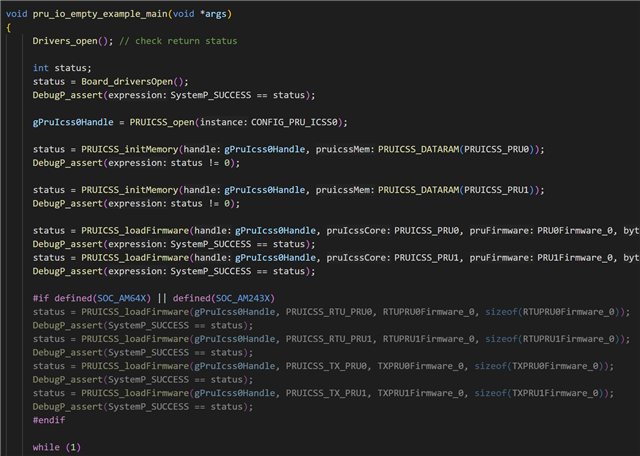

- I am trying to trigger input interrupts for 12 GPIOs. 2 of them are MUX interrupts, while the other 10 are distributed across 6 banks. Therefore, I would need 8 interrupt condition instances. Can multiple instances use the same interrupt condition, because I’ve been getting errors what I try to do that.

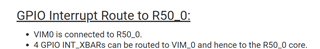

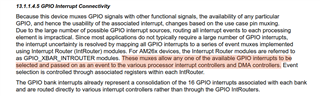

- If not, is one core only able to handle four interrupt conditions (for example for core 0 it would be R5FSS0_CORE0_INTR_GPIO_INTRXBAR_OUT_14 to R5FSS0_CORE0_INTR_GPIO_INTRXBAR_OUT_17 which correspond to xbar instances GPIO_INT_XBAR_VIM_MODULE0_0 to GPIO_INT_XBAR_VIM_MODULE0_3)? Or are there other interrupt conditions that I can choose from? And if I do have other interrupt conditions to choose from, what would be their corresponding XBar Instance?

- What are the other types of xbar instances used for (such as GPIO_INT_XBAR_ICSS_XBAR_0)

Thank You!

Saanvi