Tool/software:

Hi all,

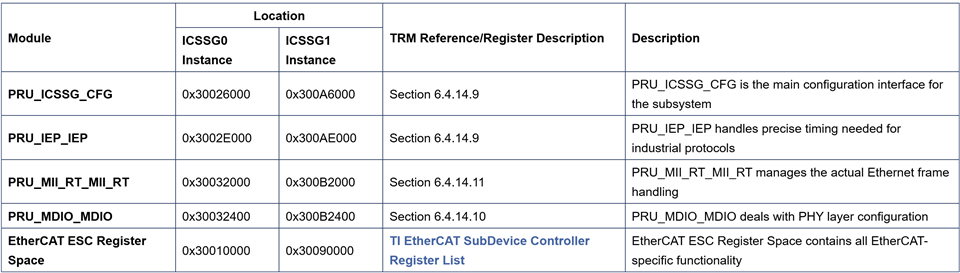

We are currently using AM2434 ALV MCU with DP83822 PHY for EtherCAT Communication. We have encountered some issues.

Environment Configuration:

- Chip: AM2434

- PHY: DP83822

- SDK Version: mcu_plus_sdk_am243x_08_06_00_45

-

EtherCAT Firmware Version: g_v1.3 (path: \mcu_plus_sdk_am243x_08_06_00_45\source\industrial_comms\ethercat_slave\icss_fwhal\firmware\g_v1.3)

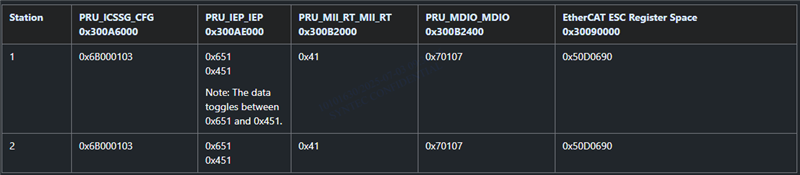

Testing method: The Master is connected to two Slave stations to perform power on/off testing.

- topology: Master → Station 1 ( AM2434 with DP83822 ) → Station 2 ( AM2434 with DP83822 )

- Power On/Off Test Description: After the Master successfully connects with Station 1 and Station 2, all three devices are powered off simultaneously. Then, they are powered on simultaneously again, and the connection is checked to confirm if it is restored properly. This cycle is repeated continuously to verify the stability of the power on/off process.

Issue Description: During the test cycles, after powering on, the Master occasionally fails to establish a connection with Station 2. At the time of the issue, the Master successfully connects with Station 1 but cannot connect with Station 2. Observing Station 2 shows that the LINK status is not established.

Slave Initialization Process:

- Our initialization process is based on the example code settings (path: \mcu_plus_sdk_am243x_08_06_00_45\examples\industrial_comms\ethercat_slave_beckhoff_ssc_demo\am243x-evm).

- The only difference is that we use the DP83822 PHY, so the configuration in tiesc_ethphyInit is slightly different. Below is the description of the configuration process adopted for the DP83822:

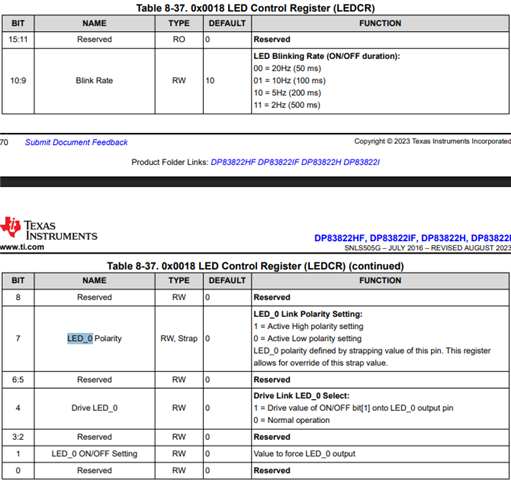

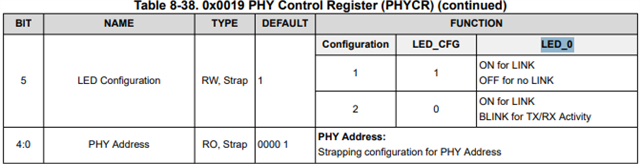

- Set PHYCR to 0x0019: Enable bits 5 and 15

- Set ANAR to 0x0004: Enable bits 0, 6, 7, and 8

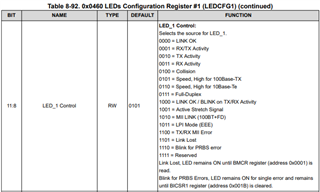

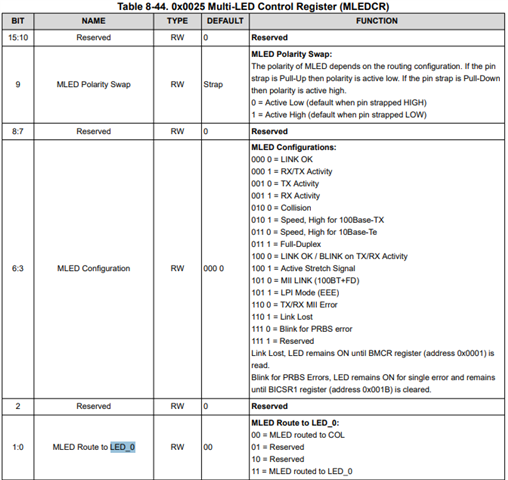

- Set IOCTRL1 to 0x0462: Configure LED_1 GPIO Configuration as 001 LED_1 (Default: Speed, High for 100Base-TX)

- Set LEDCFG1 to 0x0460: Configure LED_1 Control as 0001 RX/TX Activity

- Enable the MDIO Link change interrupt (MDIO_LINKSEL_MLINK_MODE)

- Set RCSR to 0x0017: Select MII mode

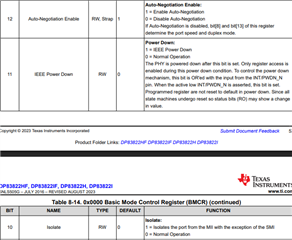

- Set BMCR to 0x0000: Enable bit 12

- Set BMCR to 0x0000: Enable bit 9

Preliminary Investigation:

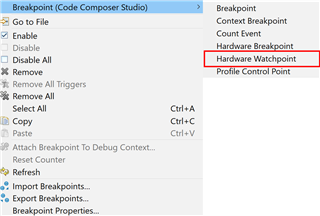

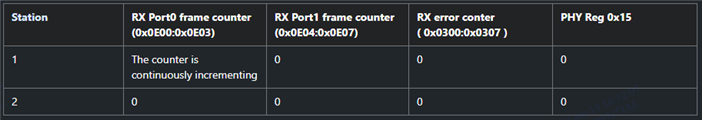

- During the occurrence of the issue, we performed the following tests:

- Restarting only Station 1, the PHY A connection of Station 1 recovered normally.

- Restarting only Station 2, the PHY A LINK status of Station 1 remained erroneous.

- We then changed the connection order of the two stations to Master → Station 2 → Station 1, and performed the power on/off cycle test. After this, the abnormal condition changed to an intermittent failure to establish a connection with Station 2, with Station 2’s PHY A LINK status not established. Even when replacing with different Slave devices (such as AM2434 + DP83822), as long as the Master is connected to multiple stations, the problem always occurs at the first station, with PHYA LINK not established. Therefore, we suspect this issue is unrelated to the hardware itself.

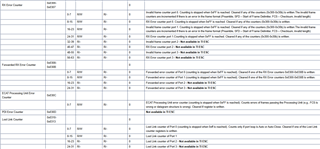

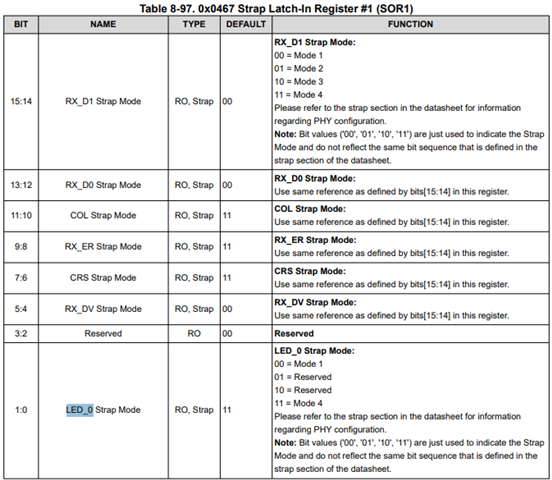

- During the occurrence, we read the PHY registers at run time and found abnormal settings in Station 1’s PHY A, with the following values:

During the issue, PHY registers were read at run time Station1 Station2 PHY REG PHYB PHYA PHYIDR2 0x0003 41536 41536 PHYCR 0x0019 35875 32802 ANAR 0x0004 449 449 IOCTRL1 0x0462 8192 8192 LEDCFG1 0x0460 12544 7168 APDC 0x041F 0 0 RCSR 0x0017 73 65 BMCR 0x0000 12544 7168 BMSR 0x0001 30829 30793 內容 PHYB PHYA PHYIDR2 0x0003 41536 41536 PHYCR 0x0019 32803 35874 ANAR 0x0004 449 449 IOCTRL1 0x0462 8192 8192 LEDCFG1 0x0460 12544 12544 APDC 0x041F 0 0 RCSR 0x0017 65 65 BMCR 0x0000 12544 12544 BMSR 0x0001 30793 30829

During normal communication, PHY registers were read at run time Station1 PHY REG PHYB PHYA PHYIDR2 0x0003 41536 41536 PHYCR 0x0019 35875

35874 ANAR 0x0004 449 449 IOCTRL1 0x0462 8192 8192 LEDCFG1 0x0460 12544 12544 APDC 0x041F 0 0 RCSR 0x0017 65 65 BMCR 0x0000 12544 12544 BMSR 0x0001 30829 30829 - After completing the

tiesc_ethphyInitconfiguration, we read back the PHY registers to verify the settings were correct. However, we still occasionally encounter abnormal behavior with Station 1’s PHY A. - We observed that the abnormal PHY register values usually occur when the ESC AL Status (0x0130) is in the Init State—that is, before EtherCAT enters the OP State. The issue appears prematurely.

Regarding the EtherCAT power on/off test with multiple stations connected to the AM2434, we occasionally see abnormal behavior with the DP83822 PHY on Station 1.

Could you please advise what might cause this issue? Are there recommended debugging and troubleshooting steps we could follow?

Best Regards,

Wei