Part Number: AM2634

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

hi TI,

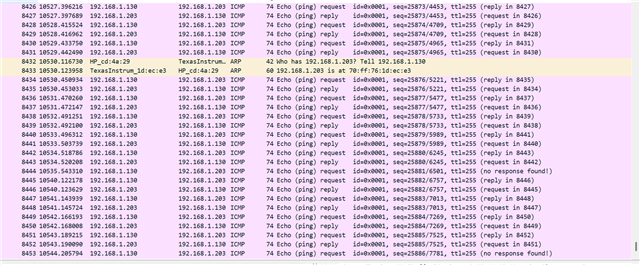

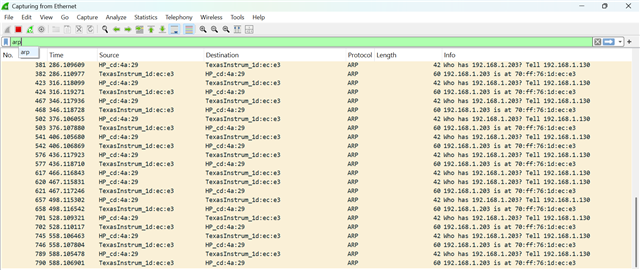

I was working on ethernet in our own customized board for pinging 2 ips we are using the phy DP83822 and i am using version 10.2.00.13 so in that i am using the example code enet_cpsw_rawhttpserver_am263x-cc_r5fss0-0_nortos_ti-arm-clang.

Our bootstrap resistor settings given below:

| Phy-0 | Phy-1 | |||

| RH | RL | Rh | Rl | |

| Rx_ERR | open | open | open | open |

| Rx_DV | 2.49 | open | 2.49 | open |

| CRS | 13K | 1.96K | 13K | 1.96K |

| COL | open | 1.96K | open | open |

| Rx_D3 | 10K | 2.49k | 10K | 2.49k |

| Rx_D0 | open | open | 2.49 | open |

| Led | open | open | open | open |

| Rx_D1 | open | open | open | open |

| Rx_D2 | open | open | open | open |

After we checked the reference clock we are getting 3Mhz - 5Mhz

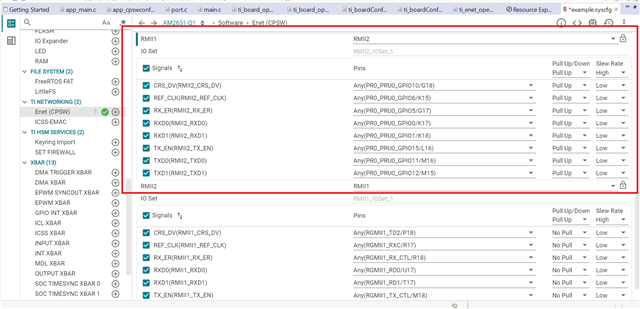

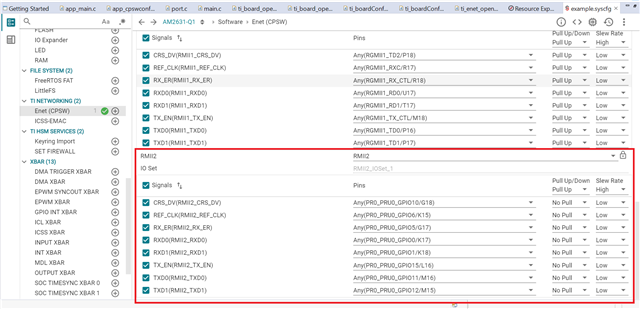

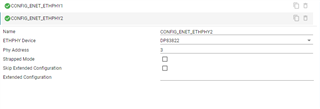

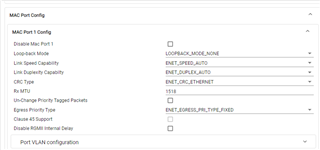

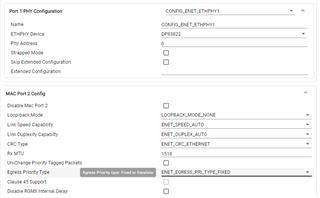

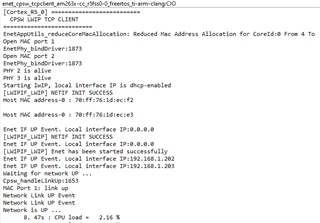

below are the sysconfig configurations:

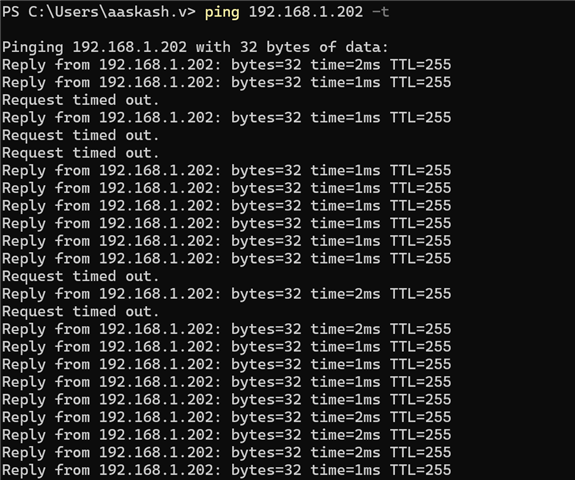

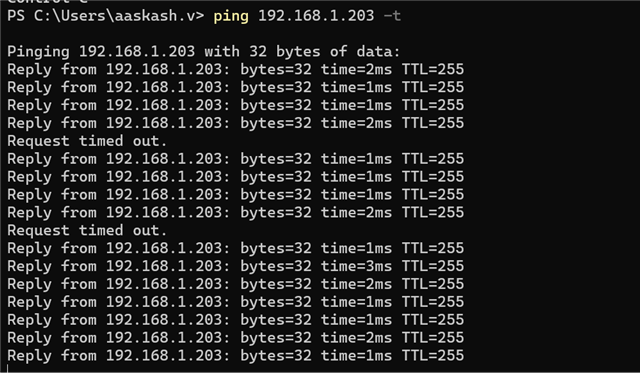

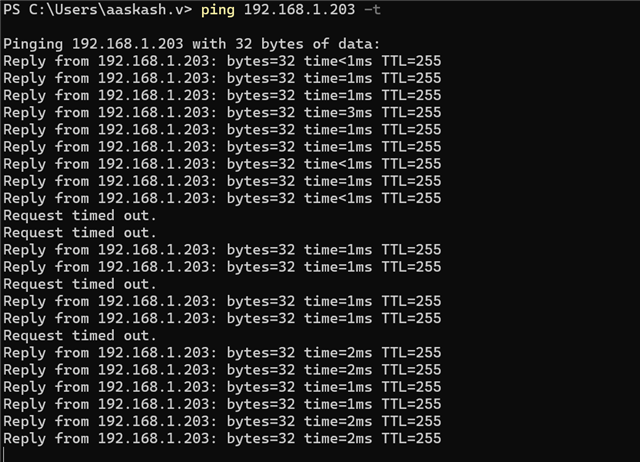

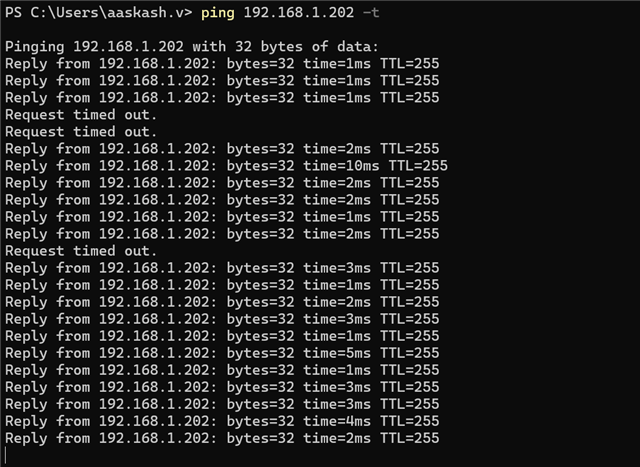

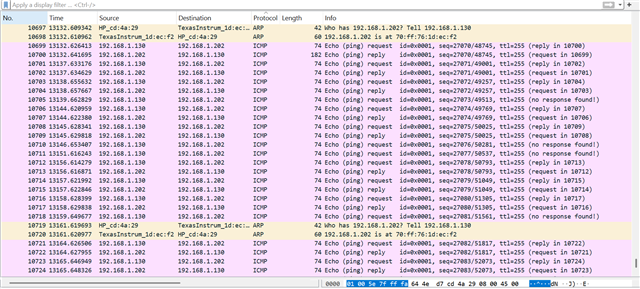

we can't be able to ping ips using this above configuration can you say what i need to do for this and we are using the below config for the bootstrap resistor.

1. can you explain what is the resistor value which i need to set for bootstrap resistor for both the phy address 1 and 3.

2. what i need to set in the sysconfig configurations.

your response is mostly welcome

Thank you,

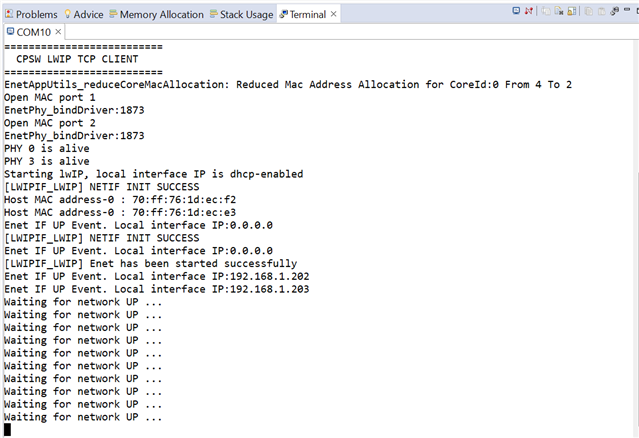

in auto assign we couldn't able to ping the any ip's

in auto assign we couldn't able to ping the any ip's