Part Number: AM2434

Tool/software:

Hello

I am currently using the PRU in SD Mode. To use GPIOs, I have to rely on the General-Purpose Interface (GPIO). My issue is that the timing of these external peripherals is less precise and shows some unusual behavior.

The test program is quite simple and generates a PWM signal. Pin multiplexing is handled by an R5F program, following the configuration described in the corresponding FAQ article, using the same settings.

LDI R1.w2, 0x60

LDI R1.w0, 0x1000 ;GPIO1 Baseaddress (0x601000)

LDI R2.w0, 0x18 ;GPIO_SET_DATA01 offset

LDI R3.w0, 0x1C ;GPIO_CLR_DATA01 offset

LDI R4.w0, 0x01 ;bit 1 -> output 0

CHECK_PROCESSING_TIMING:

SBBO &R4, R1, R2, 4 ;set General-Purpose Interfaces connected Pin High

SET R30, R30, 1 ;set PRU connected Pin 1 High

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

SBBO &R4, R1, R3, 4 ;set General-Purpose Interfaces connected Pin Low

CLR R30, R30, 1 ;set PRU connected Pin 1 Low

NOP

NOP

NOP

NOP

NOP

NOP

NOP

NOP

JMP CHECK_PROCESSING_TIMING

HALT

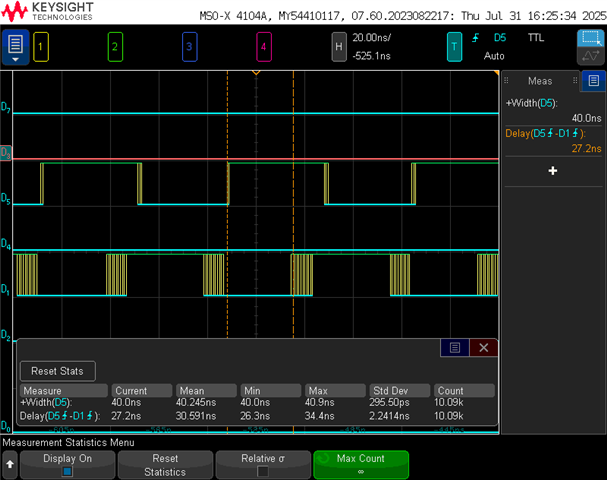

When the timing is correct, as demonstrated in the example code, the signal from the General-Purpose Interface shows a delay of approximately 27ns plus one clock cycle (3.3ns) with acceptable jitter. However, if I remove just one operation from the loop and the period no longer aligns with some internal timing of the SoC, I observe significant jitter in the General-Purpose Interface output. The standard deviation is 2.24ns, and the delay can vary between 26.3 and 34.4ns plus one clock cycle (3.3ns).

Is there a way to achieve always the better timing performance when using the PRU with the General-Purpose Interface?

Regards

Niklas