Part Number: SW-EK-TM4C1294XL

Other Parts Discussed in Thread: REF2033, TM4C1294KCPDT, TM4C1294NCPDT

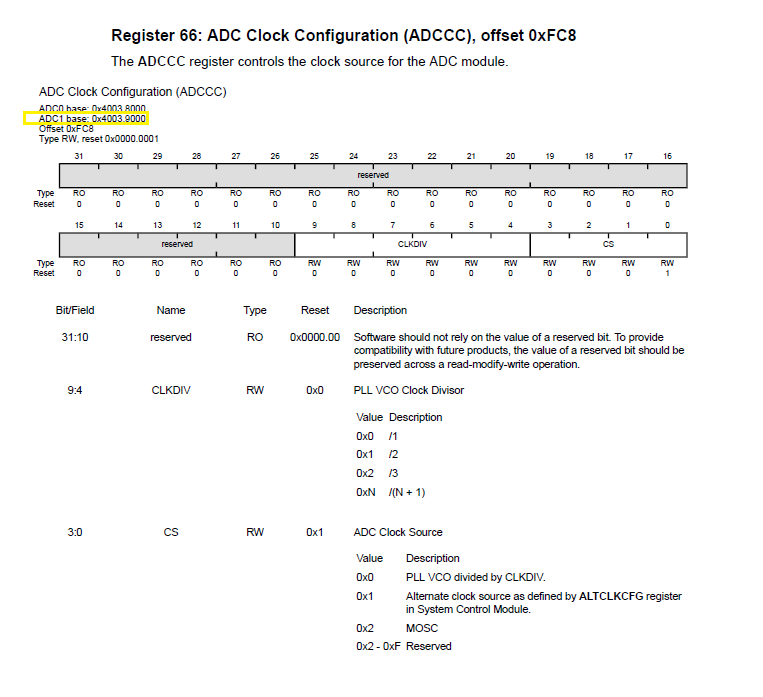

Strange issues of ADC1 temperature sensor reads and other unexplained sequencers behavior may be clock related. Past reading datasheet 15.3.2.7 states ADC0 sets the clock for the ADC module via ADCCC REG66. Most people would never think to check REG 66 that counters that statement when configuring the ADC clock via ADCClockConfigSet(). The ADC module contains both ADC0 and ADC1 blocks or peripherals. Seemingly the default ADC1 clock divisor 1 produces ADCCLK at PLL speed if it is not being configured, that is if REG 66 base address 0x4003.9000 is actually valid.

Register 66 showing ADC1 base address makes 15.3.2.7 statement odd when ADCClockConfigSet() is only called to configure ADCCC REG66 for 0x4003.8000 ADC module. It would seem a Typo exists to say ADC0 sets the modules clock most anyone believes refers to both ADC blocks. Recently discovered ADC1 base address too exists REG66 and ADCClockConfigSet() was called only once with ADC0 base address.

15.3.2.7 Module Clocking:The system clock must be at the same frequency or higher than the ADC clock. All ADC modules share the same clock source to facilitate the synchronization of data samples between conversion units, the selection and programming of which is provided by ADC0's ADCCC register. The ADC modules do not run at different conversion rates.

Do ADC0 and ADC1 blocks share the ADC modules same clock source or are the actually independent configured clock sources as being indicated in REG-66? Perhaps another good reason to illustrate the clock sources in the figures of peripheral blocks!