Part Number: TMDSECATCNCD379D

Other Parts Discussed in Thread: C2000WARE, CONTROLSUITE

Hi,

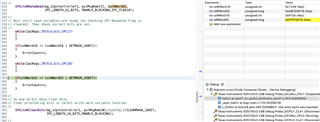

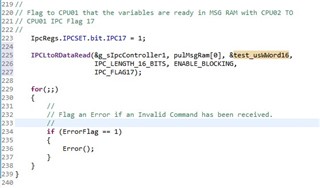

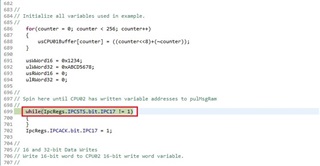

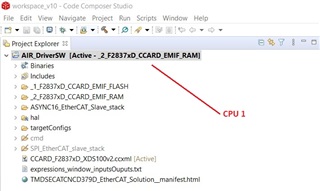

I want to communicate with EtherCAT using dual CPU. I did EtherCAT communication for CPU 1 in DSP. I want to define CPU 2 to DSP and send EtherCAT data from CPU 1 to CPU 2. Also, I will communicate with the driver use the SPI or CAN communication protocol in CPU 2.

I am waiting for your help.

Good days.