- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I'm in the process of integrating an SPI encoder (IC-Haus MU150) to the Launchpad-F28379D

I downloaded C2000Ware and modified the SPI Example project 3 "spi_ex3_external_loopback_fifo_interrupts.c"

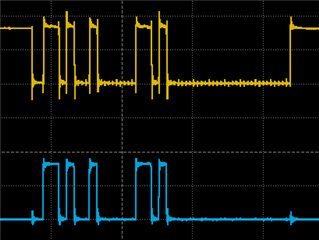

Both in debug-console and Oscilloscope measurements, I see the encoder SOMI (Yellow) echoing in the SIMO line and not sending any useful data back

Also, the SPISTEB pin seems to stay pulled down not making any signals.

Here is the code I am using

#include "driverlib.h"

#include "device.h"

/* MU150 masks */

#define MU150_OP_SDAD 0xA6

#define MU150_OP_REG_STATUS_DATA 0xAD

#define MU150_OP_WRITE_REG 0xD2

#define MU150_STATUS_VALID 0x01

#define MU150_SDAD_VALID 0x00

#define MU150_OP_READ_REG 0x97

#define MU150_ADDR_ACC_STAT 0x0D

#define MU150_ACC_STAT_BIT (0x01 << 7U)

#define MU150_ADDR_STATUS0 0x76

#define MU150_AM_MIN_BIT (0x01 << 0U)

#define MU150_AM_MAX_BIT (0x01 << 1U)

#define MU150_AN_MIN_BIT (0x01 << 2U)

#define MU150_AN_MAX_BIT (0x01 << 3U)

#define MU150_NON_CTR_BIT (0x01 << 3U)

#define MU150_EPR_ERR (0x01 << 6U)

#define MU150_ADDR_STATUS1 0x77

#define SPI_PACKET_SIZE (4U)

#define MU150_ADDR_FILT 0x0e

#define MU150_FILT1 0x01

#define MU150_FILT3 0x03 // 27dB

#define MU150_FILT4 0x04 // 39dB

#define MU150_FILT5 0x05 // 45dB

//

// Globals

//

volatile uint16_t sData[4]; // Send data buffer

volatile uint16_t rData[4]; // Receive data buffer

volatile uint16_t rDataPoint = 0; // To keep track of where we are in the

volatile uint16_t exe_rx = 0;

volatile uint16_t exe_tx = 0; // data stream to check received data

//

// Function Prototypes

//

void initSPIBMaster(void);

void initSPIASlave(void);

void configGPIOs(void);

__interrupt void spibTxFIFOISR(void);

__interrupt void spibRxFIFOISR(void);

//

// Main

//

void main(void)

{

uint16_t i;

//

// Initialize device clock and peripherals

//

Device_init();

//

// Disable pin locks and enable internal pullups.

//

Device_initGPIO();

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Interrupts that are used in this example are re-mapped to ISR functions

// found within this file.

//

Interrupt_register(INT_SPIB_TX, &spibTxFIFOISR);

Interrupt_register(INT_SPIB_RX, &spibRxFIFOISR);

//

// Configure GPIOs for external loopback.

//

configGPIOs();

//

// Set up SPI B as master, initializing it for FIFO mode

//

initSPIBMaster();

//

// Set up SPI A as slave, initializing it for FIFO mode

//

//initSPIASlave();

//

// Initialize the data buffers

//

//sData[0] = MU150_OP_WRITE_REG;

// sData[1] = MU150_ADDR_ACC_STAT;

// sData[2] = MU150_ACC_STAT_BIT;

sData[0] = MU150_OP_WRITE_REG;

sData[1] = MU150_ADDR_ACC_STAT;

sData[2] = MU150_ACC_STAT_BIT;

sData[3] = 0;

rData[0]=0;

rData[1]=0;

rData[2]=0;

rData[3]=0;

//

// Enable interrupts required for this example

//

Interrupt_enable(INT_SPIB_TX);

Interrupt_enable(INT_SPIB_RX);

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

sData[0] = 0xA6;

sData[1] = 0;

sData[2] = 0;

sData[3] = 0;

//

// Loop forever. Suspend or place breakpoints to observe the buffers.

//

while(1)

{

;

}

}

//

// Function to configure SPI B as master with FIFO enabled.

//

void initSPIBMaster(void)

{

//

// Must put SPI into reset before configuring it

//

SPI_disableModule(SPIB_BASE);

//

// SPI configuration. Use a 500kHz SPICLK and 16-bit word size.

//

SPI_setConfig(SPIB_BASE, DEVICE_LSPCLK_FREQ, SPI_PROT_POL0PHA0,

SPI_MODE_MASTER, 500000, 32);

SPI_disableLoopback(SPIB_BASE);

SPI_setEmulationMode(SPIB_BASE, SPI_EMULATION_FREE_RUN);

//

// FIFO and interrupt configuration

//

SPI_enableFIFO(SPIB_BASE);

SPI_clearInterruptStatus(SPIB_BASE, SPI_INT_TXFF);

SPI_clearInterruptStatus(SPIB_BASE, SPI_INT_RXFF);

SPI_setFIFOInterruptLevel(SPIB_BASE, SPI_FIFO_TX1, SPI_FIFO_RX1);

SPI_enableInterrupt(SPIB_BASE, SPI_INT_TXFF);

SPI_enableInterrupt(SPIB_BASE, SPI_INT_RXFF);

//

// Configuration complete. Enable the module.

//

SPI_enableModule(SPIB_BASE);

}

//

// Configure GPIOs for external loopback.

//

void configGPIOs(void)

{

//

// This test is designed for an external loopback between SPIA

// and SPIB.

// External Connections:

// -GPIO25 and GPIO17 - SPISOMI

// -GPIO24 and GPIO16 - SPISIMO

// -GPIO27 and GPIO19 - SPISTE

// -GPIO26 and GPIO18 - SPICLK

//

//

// GPIO17 is the SPISOMIA.

//

//

// GPIO25 is the SPISOMIB.

//

GPIO_setMasterCore(64, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_64_SPISOMIB);

GPIO_setPadConfig(64, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(64, GPIO_QUAL_ASYNC);

//

// GPIO24 is the SPISIMOB clock pin.

//

GPIO_setMasterCore(63, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_63_SPISIMOB);

GPIO_setPadConfig(63, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(63, GPIO_QUAL_ASYNC);

//

// GPIO27 is the SPISTEB.

//

GPIO_setMasterCore(66, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_66_SPISTEB);

GPIO_setPadConfig(66, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(66, GPIO_QUAL_ASYNC);

//

// GPIO26 is the SPICLKB.

//

GPIO_setMasterCore(65, GPIO_CORE_CPU1);

GPIO_setPinConfig(GPIO_65_SPICLKB);

GPIO_setPadConfig(65, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(65, GPIO_QUAL_ASYNC);

}

//

// SPI A Transmit FIFO ISR

//

__interrupt void spibTxFIFOISR(void)

{

uint16_t i;

//

// Send data

//

for(i = 0; i < 4; i++)

{

SPI_writeDataNonBlocking(SPIB_BASE, sData[i]);

}

//exe_tx++;

//

// Increment data for next cycle

//

//

// Clear interrupt flag and issue ACK

//

SPI_clearInterruptStatus(SPIB_BASE, SPI_INT_TXFF);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP6);

}

//

// SPI B Receive FIFO ISR

//

__interrupt void spibRxFIFOISR(void)

{

uint16_t i;

//

// Read data

//

for(i = 0; i < 4; i++)

{

rData[i] = SPI_readDataNonBlocking(SPIB_BASE);

}

//exe_rx++;

//

// Check received data

//

//

// Clear interrupt flag and issue ACK

//

SPI_clearInterruptStatus(SPIB_BASE, SPI_INT_RXFF);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP6);

}

//

// End of File

//Can someone help me spot error in this? Perhaps incorrect logic flow with interrupts?

Thanks

Hansol

I downloaded C2000Ware and modified the SPI Example project 3 "spi_ex3_external_loopback_fifo_interrupts.c"

Both in debug-console and Oscilloscope measurements, I see the encoder SOMI (Yellow) echoing in the SIMO line and not sending any useful data back

I suspect that the internal loopback functionality maybe enabled for the SPI. That is the first thing I suggest checking.

Best regards

Lori

Hi Lori,

The example code was for the external loopback, so the internal loopback function was disabled from the beginning. (line 158 SPI_disableLoopback())

Another concern that I have is that the STE(chip select pin) is not enabled even when it is configured at Line 217. The osciliscope reading shows that it is constantly low. I suspect this might be causing some issues. Any idea why this would happen?

Thanks

Hansol

Another concern that I have is that the STE(chip select pin) is not enabled even when it is configured at Line 217. The osciliscope reading shows that it is constantly low. I suspect this might be causing some issues

The SPI will automatically control the SPISTE pin. It will drive the SPISTE pin low during a transfer, and drive it high after the transfer is done. Are you observing the pin low, even after a transfer is complete?

If this pin never goes high (inactive) then first check that nothing on the board is holding it low. Can you toggle the pin it if it is a GPIO?

One thing to note - If your code keeps data in the TXFIFO. As long as there is data to transmit, SPISTE will stay low. If you want to force SPISTE to return high after each 16-bit word, you can disable the FIFO and send one word at a time until the SPI_INT bit is set, indicating that 16 bits have been transmitted.