Part Number: TMS320F280049C

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

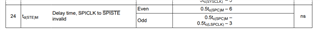

when baudrate set to 3.125MHz or 1MHz, use fifo mode set the delay between fifo to shift register to 0, the STE remain low in the whole process

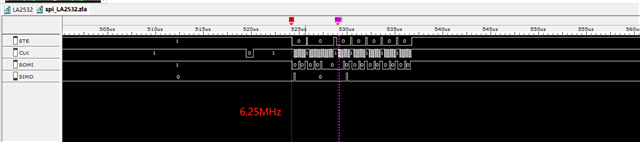

when buadrate up to 6.25Mhz or 12.5MHz, STE will back to high for a few spi cycle, this coud affect data back on the SOMI line, how can i solve it