Hello!

I have one question that puzzled me for a long time , about EPWM:

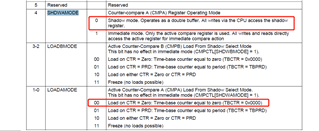

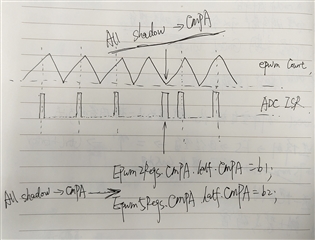

As shown above, high level means ADC ISR, if I update PWM register value Every cycle in this ADC ISR, and I use PWM compare shadow register, C code is like this:

interrupt void ADCISR(void)

{

....

EPwm1Regs.CMPA.half.CMPA = a1;

EPwm4Regs.CMPA.half.CMPA = a2;

EPwm2Regs.CMPA.half.CMPA = b1; //<------------------------

EPwm5Regs.CMPA.half.CMPA = b2;

EPwm3Regs.CMPA.half.CMPA = c1;

EPwm6Regs.CMPA.half.CMPA = c2;

...

}

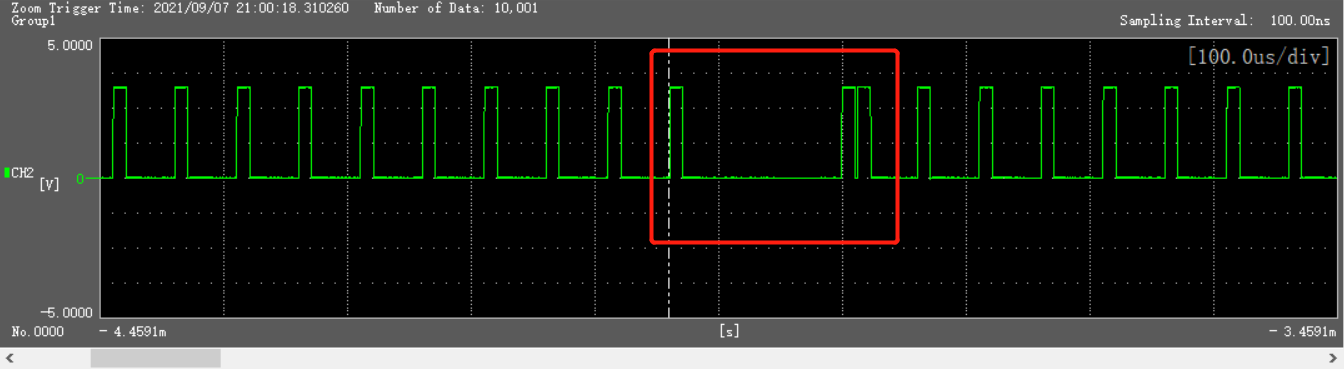

As you see, ADC ISR should be strictly executed once at 50us, but because freemodbus closed the global interrupt when processing a frame of data, the ADC ISR was delayed. As shown in the red box.

So, In this case, is there such a possibility: when DSP Finished "EPwm2Regs.CMPA.half.CMPA = b1;" , PWM transfers the values of all shadow registers to the PWM action registers, which causes the value of "EPwm2Regs.CMPA.half.CMPA" to be the result of a new cycle calculation, while the value of "EPwm5Regs.CMPA.half.CMPA" is still the previous cycle result of the calculation. If these two PWMs control the upper and lower tubes of the same bridge , is there a possibility that the upper and lower bridge are directly connected?