Other Parts Discussed in Thread: TMDSEMU110-U

Hi experts,

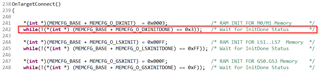

In customer's field, the TMDSEMU110-U debug probe can't connect to the target and prompts that the device is in low-power mode.

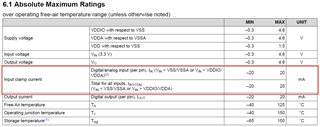

We find that when 3.3V VDDIO has larger voltage ripple (ripple = ±0.2V, due to connecting to IGBT driver board), the above phenomenon will happen. But when not connecting the driver board, the 3.3V VDDIO is smoother, and the debugger can work as expected.

So I want to know the root cause of this failed target-connection, due to MCU itself or XDS110 debugger or both? What is the tolerated voltage ripple for DSP and XDS110 debugger to work fine?

Best Regards,

Will