Other Parts Discussed in Thread: PGA411-Q1

Hello,

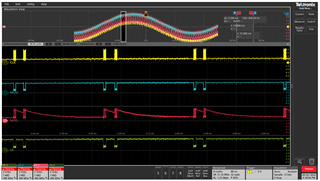

I have my project mostly working with the TMS320F280039C and just a couple issues are holding me back from going to testing with this microcontroller. I am using the MCU to control an AC motor and have the motor spinning. The way my project is structured I have a 250us ADC interrupt that fires and does my motor control. This interrupt then fires off a user interrupt that runs for 100us (note that the added 100us must be less than 250us total). During the 250us interrupt I use SPI FIFO interrupts to read my resolver twice. This is working well, but I seem to be getting some bad data back causing noise in my speed feedback and an audible noise in my motor sometimes since I am firing current at the incorrect spot.

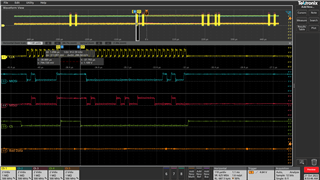

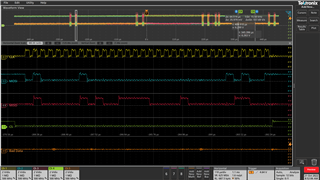

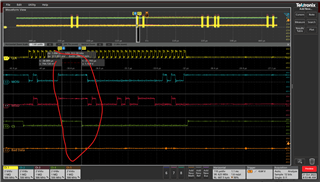

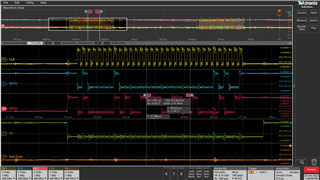

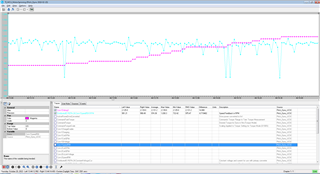

Below Conv1Debug3 shows a count of bad data on the SPI link - as can be seen in 1.5s I missed 14 transfers from my resolver and you can also notice the accompanying glitches in speed:

I wonder if this is a nested interrupt issue?

I am starting a SPI transfer like this - note that I had to add EINT to allow 2 SPI interrupts during my ADC ISR.

// Start sequence of SPI Master read/write register operations to Resolver chip - Blocking

void SpiMaster_StartTransfer(GE_Primary_Container_t *pContainer, uint32_t command)

{

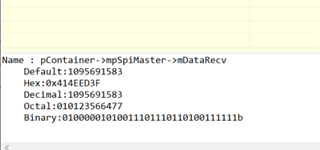

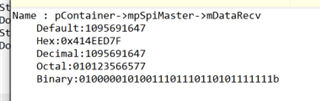

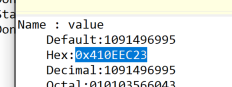

pContainer->mpSpiMaster->mDataRecv = 0;

// Reset Rx and Tx Buffers

SPIMaster_ResetBuffers(pContainer);

// Set TxData buffer

pContainer->mpSpiMaster->mTxData[0] = (command >> 24) & 0xFFU;

pContainer->mpSpiMaster->mTxData[1] = (command >> 16) & 0xFFU;

pContainer->mpSpiMaster->mTxData[2] = (command >> 8) & 0xFFU;

pContainer->mpSpiMaster->mTxData[3] = (command & 0xFFU);

pContainer->mpSpiMaster->mIsTransferCompleted = false;

// Reset / Setup SPI

SPIMaster_SetupResetSPI(pContainer);

// Reset / Setup FIFO

SPI_disableFIFO(REPC_RES_DSPI_MASTER_BASEADDR);

SPI_clearInterruptStatus(REPC_RES_DSPI_MASTER_BASEADDR, SPI_INT_TXFF);

SPI_clearInterruptStatus(REPC_RES_DSPI_MASTER_BASEADDR, SPI_INT_RXFF);

SPI_enableFIFO(REPC_RES_DSPI_MASTER_BASEADDR);

SPI_setFIFOInterruptLevel(REPC_RES_DSPI_MASTER_BASEADDR, SPI_FIFO_TXEMPTY, SPI_FIFO_RX4);

// Enable RxFIFO Interrupt

SPI_enableInterrupt(REPC_RES_DSPI_MASTER_BASEADDR, SPI_INT_RXFF);

// Enable SPI

SPI_enableModule(REPC_RES_DSPI_MASTER_BASEADDR);

// Clear INTM so that we can trigger another interrupt inside of fast thread

EINT;

// Enable interrupts

Interrupt_enable(INT_SPIB_TX);

Interrupt_enable(INT_SPIB_RX);

// Fill FIFO and send data - no interrupt required here

int i = 0;

for (i = 0; i < REPC_RES_MASTER_TRANSFER_SIZE; i++)

{

SPI_writeDataNonBlocking(REPC_RES_DSPI_MASTER_BASEADDR, ((pContainer->mpSpiMaster->mTxData[i] & 0x00FF) << 8));

}

}

This is how I have the SPI initialized:

// Setup / Reset SPI

void SPIMaster_SetupResetSPI(GE_Primary_Container_t *pContainer)

{

// Must put SPI into reset before configuring it

SPI_disableModule(REPC_RES_DSPI_MASTER_BASEADDR);

// SPI configuration. Use a 12.5MHz SPICLK and 32-bit word size, 25MHz LSPCLK

// Rising edge SPI

SPI_setConfig(REPC_RES_DSPI_MASTER_BASEADDR, REPC_RES_DSPI_MASTER_CLK_SRC, SPI_PROT_POL0PHA0,

SPI_MODE_MASTER, REPC_RES_TRANSFER_BAUDRATE, 8U);

SPI_disableLoopback(REPC_RES_DSPI_MASTER_BASEADDR);

SPI_setEmulationMode(REPC_RES_DSPI_MASTER_BASEADDR, SPI_EMULATION_FREE_RUN);

}

// Init SPI1 Interface to resolver

void SPIMaster_Init(GE_Primary_Container_t *pContainer)

{

// Register interrupt ISRs

Interrupt_register(INT_SPIB_TX, &spiBTxFIFOISR);

Interrupt_register(INT_SPIB_RX, &spiBRxFIFOISR);

// Setup / Reset SPI

SPIMaster_SetupResetSPI(pContainer);

// Configuration complete. Enable the module.

SPI_enableModule(REPC_RES_DSPI_MASTER_BASEADDR);

// Init Master Buffers to 0

SPIMaster_ResetBuffers(pContainer);

// Init Control Variables

pContainer->mpSpiMaster->mIsTransferCompleted = false;

}

Thanks for the help!