Other Parts Discussed in Thread: TMS320F28388D, UCD9090, , UCD9090-Q1

Hello,

We are using the TMS320F28388D evaluation board to communicate with an UCD9090 through the PMBus.

We send a write byte command with PEC enabled (command PAGE of the UCD with data byte set to 1) to the UCD.

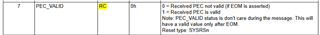

We read back the current page of the UCD by sending a read byte command with PEC enabled. We expect to check the PEC code by reading the PEC_VALID bit of PMBSTS register but this bit is never set.

The data byte received is 1 as expected.

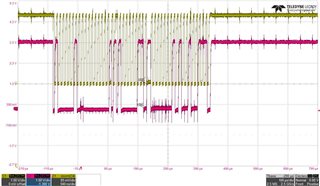

When looking at the signal on scope we can see that the PEC byte sent back by the UCD is 0x93 (which is the expected CRC that we previously computed).

PMBus peripheral is used as follow:

- ALERT and CONTROL pins not used

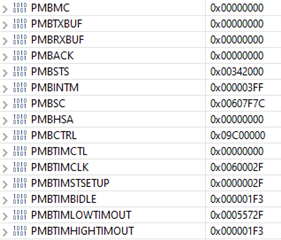

- Registers initial values:

- We launch the read byte command (command PAGE of the UCD) as described in the TRM

- We wait for the EOM by polling the status register then check the PEC_VALID bit (without re-reading the status register).

We should be able to check the PEC_VALID bit. Have we done anything wrong ?

Best regards,

Clément