Other Parts Discussed in Thread: UNIFLASH

Hello,

My program is working fine in debug mode.

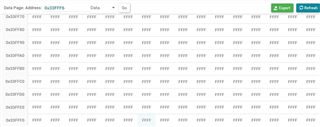

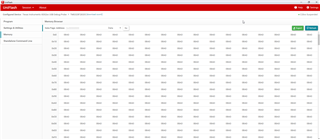

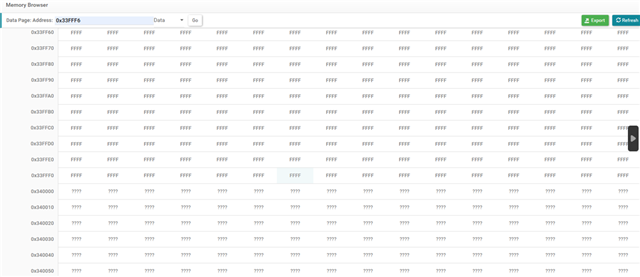

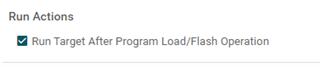

After building in Release mode, it also works fine with this option checked

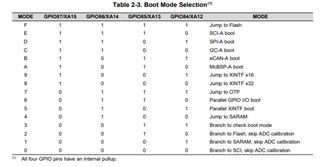

But, if I am switching off/on my DSP, the program will not run.

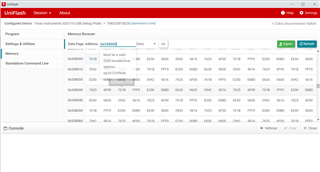

I tried updating my Uniflash Software, as I saw in a forum but it didn't work.

I hope I will find help, thank you very much.

Best Regards

Mattéo