void ConfigEpwm(void)

{

#ifdef CODE_MASTER

EALLOW;

SyncSocRegs.SYNCSELECT.bit.SYNCOUT = 0x2; //select epwm7 sync signal to syncout

//config gpio24 for output xbar1

GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 1;//mux: output xbar1

GpioCtrlRegs.GPAPUD.bit.GPIO24 = 1; //disable pull-up

GpioCtrlRegs.GPADIR.bit.GPIO24 = 1;//output

//config gpio25 for output xbar2

GpioCtrlRegs.GPAPUD.bit.GPIO25 = 1; //disable pull-up

GpioCtrlRegs.GPADIR.bit.GPIO25 = 1;//output

GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 1;//mux: output xbar2

//config output xbar1 for external sync out

OutputXbarRegs.OUTPUT1MUX0TO15CFG.bit.MUX14 = 0x3; //select external sync out

OutputXbarRegs.OUTPUT1MUXENABLE.bit.MUX14 = 0x1; //enable xbar mux

//config output xbar2 for external sync out

OutputXbarRegs.OUTPUT2MUX0TO15CFG.bit.MUX14 = 0x3; //select external sync out

OutputXbarRegs.OUTPUT2MUXENABLE.bit.MUX14 = 0x1; //enable xbar mux

EDIS;

#endif

#ifdef CODE_SLAVE

EALLOW;

//Config Gpio23 for syncin

GpioCtrlRegs.GPAMUX2.bit.GPIO23 = 0;

GpioCtrlRegs.GPADIR.bit.GPIO23 = 0; // gpio input

GpioCtrlRegs.GPAPUD.bit.GPIO23 = 1; //disable pull-up

GpioCtrlRegs.GPAQSEL2.bit.GPIO23 = 0; //sync input mode

//config input xbar5 to link gpio23 and EXTSYNCIN1

InputXbarRegs.INPUT5SELECT = 23;//select gpio 23

//select external sync for epwm7

SyncSocRegs.SYNCSELECT.bit.EPWM7SYNCIN = 0x5; //select EXTSYNCIN1

EDIS;

#endif

InitEPwm7Gpio();

InitEPwm8Gpio();

//pro3

EALLOW;

//Config Gpio42 PRO3 for ~TZ1

GpioCtrlRegs.GPBMUX1.bit.GPIO42 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO42 = 0; // gpio input

GpioCtrlRegs.GPBPUD.bit.GPIO42 = 1; //disable pull-up

GpioCtrlRegs.GPBQSEL1.bit.GPIO42 = 3; //async input mode

//input xbar

InputXbarRegs.INPUT1SELECT = 42;//select gpio 42

EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;//turn off epwm clk,turn on after config

// Setup TBCLK

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count upDOWM

EPwm7Regs.TBPRD = TIMER_TBPRD; // Set timer period

#ifdef CODE_MASTER

EPwm7Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

#endif

#ifdef CODE_SLAVE

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Enable phase loading

EPwm7Regs.TBCTL.bit.PHSDIR = 1; //count up after sync

#endif

EPwm7Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm7Regs.TBCTR = 0x0000; // Clear counter

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV2;

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm8Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count upDOWM

EPwm8Regs.TBPRD = TIMER_TBPRD; // Set timer period

EPwm8Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Enable phase loading

EPwm8Regs.TBPHS.bit.TBPHS = 1180; // Phase is 170 , under initial condition

EPwm8Regs.TBCTL.bit.PHSDIR = 0; //count down after sync

EPwm8Regs.TBCTR = 0x0000; // Clear counter

EPwm8Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm8Regs.TBCTL.bit.CLKDIV = TB_DIV2;

// EPwm8Regs.TBCTL.bit.SYNCOSEL=TB_CTR_ZERO;

// Setup shadow register load on ZERO

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm8Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm8Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm8Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm8Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set Compare values

EPwm7Regs.CMPA.bit.CMPA = CMPANUM; // Set compare A value

EPwm7Regs.CMPB.bit.CMPB = CMPBNUM; // Set Compare B value

EPwm8Regs.CMPA.bit.CMPA = CMPANUM; // Set compare A value

EPwm8Regs.CMPB.bit.CMPB = CMPBNUM; // Set Compare B value

// Set actions

EPwm7Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Clear PWM2A on Period

EPwm7Regs.AQCTLA.bit.CAD = AQ_SET; // Set PWM2A on event A,

// up count

EPwm7Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Clear PWM2B on Period

EPwm7Regs.AQCTLB.bit.CAD = AQ_SET; // Set PWM2B on event B // up count

EPwm8Regs.AQCTLA.bit.CAU = AQ_CLEAR; // Clear PWM2A on Period

EPwm8Regs.AQCTLA.bit.CAD = AQ_SET; // Set PWM2A on event A,

// up count

EPwm8Regs.AQCTLB.bit.CAU = AQ_CLEAR; // Clear PWM2B on Period

EPwm8Regs.AQCTLB.bit.CAD = AQ_SET; // Set PWM2B on event B, // up count

// Active Low complementary PWMs - setup the deadband

EPwm7Regs.DBCTL.bit.IN_MODE = DBA_ALL; //A:UP EDGE;B:FALL EDGE DBA_RED_DBB_FED

EPwm7Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //11:TOTAL ENABLE;00:DISABLE

EPwm7Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //10:only B invert

EPwm7Regs.DBRED.bit.DBRED = DB_DURATION; //UP DELAY

EPwm7Regs.DBFED.bit.DBFED = DB_DURATION; //FALL DELAY

EPwm8Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm8Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm8Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm8Regs.DBRED.bit.DBRED = DB_DURATION;

EPwm8Regs.DBFED.bit.DBFED = DB_DURATION;

EPwm8Regs.DBCTL.bit.OUTSWAP = 3;

//ADC trig setting

EPwm7Regs.ETSEL.bit.SOCASEL = ET_CTR_PRDZERO; //SOC event choose

EPwm7Regs.ETSEL.bit.SOCAEN = 1; //enable SOCA

EPwm7Regs.ETPS.bit.SOCAPRD = 1; //1-3times trig ADC

//TZ SETTING

EPwm7Regs.TZSEL.bit.CBC1 = 1;//select TZ1 cbc

EPwm7Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm7Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm7Regs.TZCLR.bit.CBCPULSE = 0; //cbc clear when CTR = 0

//EPwm7Regs.TZCLR.bit.OST = 1;

EPwm7Regs.TZFRC.bit.OST = 1;

EPwm8Regs.TZSEL.bit.CBC1 = 1;//select TZ1 cbc

EPwm8Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm8Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm8Regs.TZCLR.bit.CBCPULSE = 0; //cbc clear when CTR = 0

//EPwm8Regs.TZCLR.bit.OST = 1;

EPwm8Regs.TZFRC.bit.OST = 1;

EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

}

Hello!

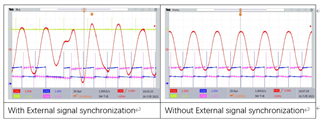

I want to use two independent DSP as the slave, and another DSP as the host, to achieve the external signal synchronization between the host and the two slave. However, when the external synchronization signal is connected, the EPWM signal output from the slave machine is not complementary, and it is normal to not connect the synchronization signal.Next is my test waveform and code.

Is there anyone who could tell me how to do that?

Thank a lot.