Part Number: TMS320F280039

Hi Team,

There's an issue from the customer need your help:

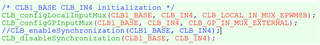

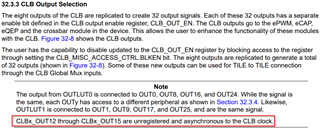

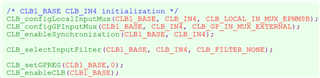

We use the CLB module in the application, the purpose is to configure EPWM8B to a specific IO pin through CLB, the IO pin itself cannot be configured as an epwm port. The configuration is as follows: The output of the EPWM8B AQ module is used as the input of CLB_IN4, and the output of CLB output6 is configured to the IO pin through the CLBoutputxbar. It is found that the driving waveform after the CLB module has a fixed delay (23ns) compared to the original epwm8B module. Is there any way to solve it? Thanks!

Best Regards,

Ben