What is the proper way to pass an output form one CLB TILE to input of another CLB TILE?

example.. Below is CLB TILE (TILE0); would like to use out0 and out 7 as input to another tile (TILE1).

TILE0:

TILE1:

For Boundary Inputs for TILE1, in syscfg I have the following:

Intention is to used TILE0 out0 as input to TILE1 i4 and TILE0 out7 as input to TILE1 i5.

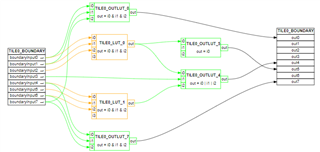

Using Simulink.. in "Hardware Implementation/Target hardware resources" am setting up CLB TILE1 inputs as shown below:

Setting IN4 and IN5 to GPREG input 0; is this correct?

When I run my model. The TILE0 out0 and out7 don't seem to pass to TILE1 i4 and i5.. I tested this by sending i4 or i5 to TILE1 out4 or out5 (out4 and out5 are sent to Output X-BAR where signal is assigned to GPIO)