Hello,

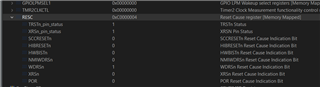

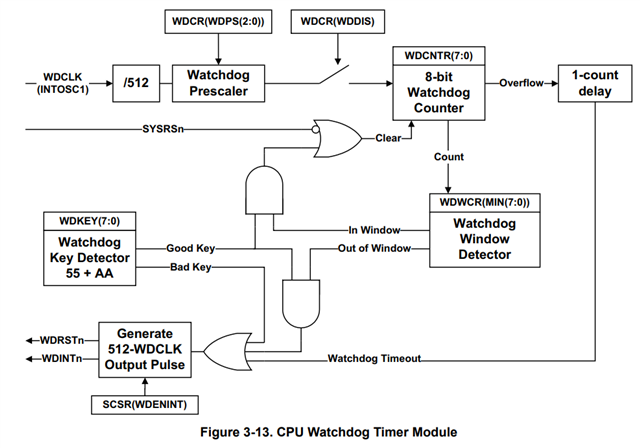

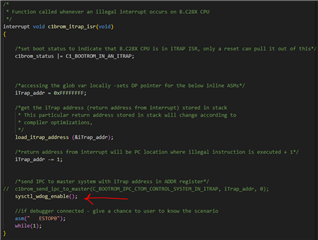

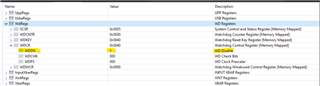

I have an application where the MCU is reset sometimes. To try to investigate the issue I am using the SysCtl_getResetCause function. The MCU is reporting a Watchdog reset (WDRSn), but the watchdog is disabled in my application (I have double-checked this in both CPUs). How is this possible?

On the other hand, I noticed that the SysCtl_getResetCause function never returns 1 (POR bit enabled). I think it should be enabled on each power cycle, so I am not sure if I can trust the function's return value.

Best regards,

Luis