- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello everyone,

I had such a doubt while studying the HRPWM application documentation, which is shown below:

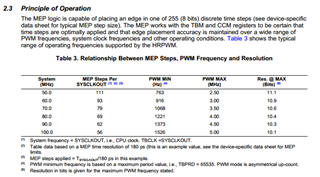

At the beginning of the document, it is described that the MEP count can be used to place the edge at 255 times, but the table only shows that the MEP_Factor Max is only 111, not 255. My question is, if you can reach 255, why can't you continue to reduce the frequency of SYSCLKOUT (that is, TBCLK) so that the MEP value is around 255, or if the minimum frequency of TBCLK can only be 50MHz and can't be lowered any further? At the same time, when the frequency of TBCLK is 50MHz, why is the maximum frequency of PWM 2.5MHz? The maximum frequency should be related to the value setting of PRD, if the maximum is 2.5MHz, then the minimum PRD value should be 20 in the up_count or down_count mode or 10 in the up_down_count mode, which can not be smaller.

But according to the documentation, isn't the PRD value arbitrary? Or does the value of PRD also have a minimum value when it is set, and the set value cannot be less than this value?

Best Regrds

Runhao

Hi Runhao,

The max user input for MEP steps will always be 255. However, the numbers in that table showcase values from internal calculations due to SFO library and autoconversion. These values are just examples showing the number of MEP steps it would take to equate to one TBCLK with autoconversion enabled. So the reason why it's not 255 is because autoconversion is internally calculating the actual number of MEP steps.

Best Regards,

Allison

Hi Allison,

Thank you for your explanation about the MEP step size, I also have a question about why the maximum frequency of PWM that can be generated when TBCLK=50MHz is 2.5MHz, in other words, the minimum value of the TBPRD register is 20, why is this? Is it because this setting produces the most accurate PWM frequency? In theory, the value of PRD can be further reduced to obtain a higher frequency PWM, but why the highest frequency given on the table is only 2.5MHz?

Best Regrds

Runhao

Hi Runhao,

There is no specific restriction on the value of TBPRD (can be from 0 to 65535) alone, but I understand the question is why is TBPRD = 20 for all the calculations in that table/is there some reasoning for that. Please allow for some time for me to contact those who generated the table to double check for you. I will update later this week or as soon as I hear from them.

Best Regards,

Allison

Hi Runhao,

Thanks for your patience.

For that table, TBPRD is just an example input parameter. The key item that the table was intended to highlight is just the RES @ MAX.

So for us to show resolution column, we need to first have the inputs to the equation, which is the PWM MAX frequency needed by the application. Without that, we cannot calculate the last column which has the resolution. The last column is technically: Minimum resolution of the HRPWM (bits) when operating at the stated PWM MAX. So for the first row: If you want to operate between 916Hz to 3MHz, with HRPWM, the least number of bits for resolution you will ever have within that PWM frequency range, will be 10.9.

Best Regards,

Allison

Hi Allison,

Thank you for your patient answer. I have understood the calculation method in this table.

Best Regrds

Runhao