Hi Team,

There's an issue from the customer need your help:

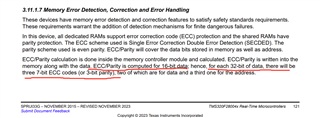

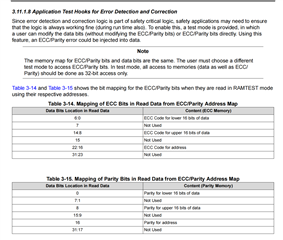

According to the reference manual, 32-bit data can be split into two 16-bit ECC codes to calculate two 7-bit ECC codes, and ask for help how the algorithm calculates. The ECC calculations I searched for were all 16-bit data that could calculate 5-bit ECC codes, so why do I need 7 bits?

But if I use the SECDED algorithm, I only need 5 bits of ECC to verify 16 bits of data, so why do I need 7 bits?

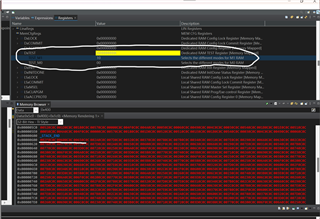

And I used the purchased 280049c board to test the M1, used the CCS tool to MemCfgRegs.DxTEST.bit.TEST_M1=2, and then according to the address map described in the user manual, I can read out that the corresponding ECC code is 0xC when the corresponding data is 0. How is this calculated?

Best Regards,

Ben