Part Number: TMS320F28386D-Q1

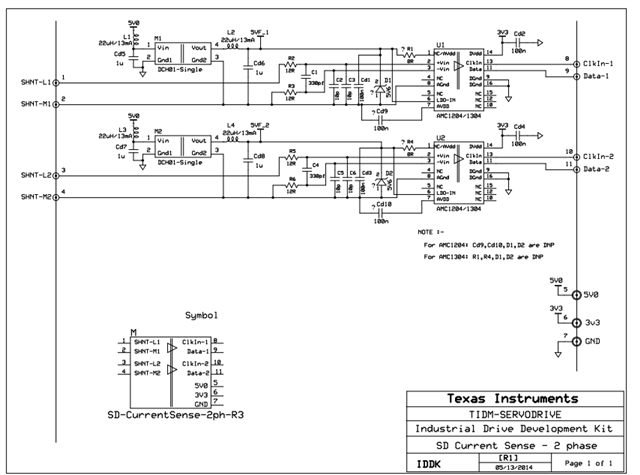

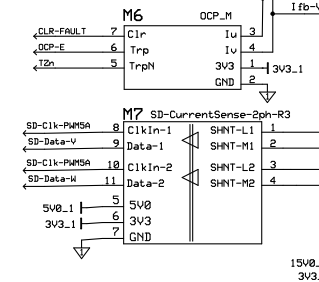

Other Parts Discussed in Thread: AMC1306M05, TIDM-SERVODRIVE, AMC1204, SYSCONFIG

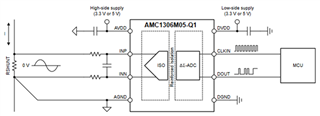

I'm working on a design with a TMS320F28386 DSP and an array of AMC1306M05 isolated sigma-delta ADCs sensing current.

I have a basic hook up question and I can't seem to find a good answer in the documentation.

Why does the F28386 datasheet refer to the SDFM clocks as inputs? They're referred to as inputs in the pin attributes table, Figure 7-36 SDFM block diagram, and in the digital signals table (Table 6-3).

I'm confused as these are obviously clock outputs that supply the modulation clock to the external sigma-delta ADCs, (as in several of the isolated sigma-delta evaluation kit examples offered by TI).

Why does the DSC documentation treat these as inputs?

Thanks,

Jason