Hello,

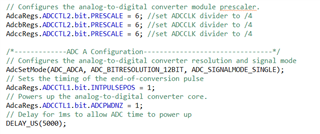

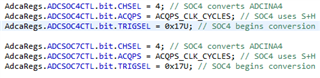

I have configured SOC4 and SOC7 for ADC bank A to sample channel 4 signal which is Phase A grid Voltage. Below is the code snippet.

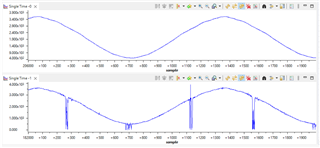

But both result register produce different results and it is dependent on the operating power level of 3-ph, 2-level active front end converter. Top is ResultReg7 and bottom is ResultReg4. Any help as to why this is happening would be really appreciated.

Regards,

Manish Kumar