Other Parts Discussed in Thread: TIDM-02014

Hello,

The phase shift for the excitation pwm is set to '2' with EPWM_setPhaseShift(RESOLVER_EXCITATION_PWM_BASE, 2); in board.c generated from syscfg in the TIDM-02014 project.

The excitation pwm is configured for up-count.

I made a couple of modifications to better visualize the concern that leads to my question.

- I configured the SYNC output pulse to be sent to an OUTPUTXBAR IO for debug/monitoring.

- I configured the EPWM to output a 50% duty waveform that I can monitor at the pin. I have the output go high at CNTR=ZERO and low at CNTR=CMPA (as is done in other examples).

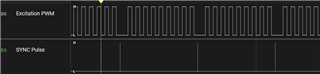

- When I do this, I see a missing pulse in the excitation PMW waveform:

The sync causes the phase load and sets CNTR=2, it does not have that CNTR=ZERO trigger to cause the output to go high. I think this is why the pulse is missed.

In the original code / setup for the excitation pwm, the interrupt trigger is also set to CNTR=ZERO in board.c: EPWM_setADCTriggerSource(RESOLVER_EXCITATION_PWM_BASE, EPWM_SOC_A, EPWM_SOC_TBCTR_ZERO);

This interrupt is used to trigger an update for the DAC. It seems like the DAC update would also be missed on sync because CNTR=ZERO is skipped when the sync causes '2' to be loaded to CNTR.

Is this a correct interpretation, that the DAC update is missed?

If yes, does it matter that the DAC update is missed?

Thanks,