- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Yun,

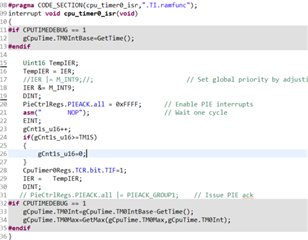

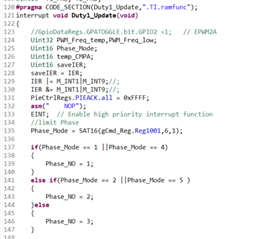

We have an interrupt SW prioritization example which demonstrates the software prioritization of interrupts through CPU Timer Interrupts. Software prioritization of interrupts is achieved by enabling interrupt nesting.

Please have a look at these threads also -

Hi Yun,

I apologize for the delay. The interrupts you are trying to use are in the following locations in the ePIE table:

EPWM1 - INT3.1

TIMER0 - INT1.7

SCIB_RX - INT9.3

Given the order in the ePIE, the below would be the priorities in hardware:

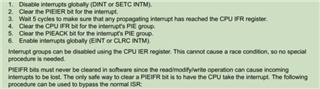

If you are ok with the priority order above but just want to allow nesting of higher priority interrupts inside lower priority interrupts, you can simply add an EINT inside your low priority ISR's. For example:

If you want to change the order of these priorities to be different than are defined in the ePIE, that is when you would need to alter the IER register and use the masking defines.

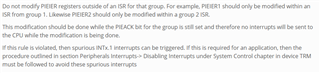

Since you are only wanting to nest interrupts that are all from different groups, no accesses to the PIEIER registers need to be made. You only need to work with the PIEIER registers if trying to change priorities within a group. For example, if you were using the TIMER0 interrupt and the XINT1 interrupt and wanted TIMER0 to have a higher priority.

Please let me know which priority order you are looking to use, and I can assist with specific code implementation if needed.

Best Regards,

Delaney

Hi Delaney,

Thank you for your patience and reply.

1.Your answers solved my questions 1 and 3. colud you please explain the 4th question in detail? I don't quite understand it. And I would like SCIB_RX ISR to be the highest priority, then TIMER0_ISR and EPWM1 last. Because I found SCI communication can be disturbed by EPWM interrupt when the EPWM period is very small.

2. For the sencond question, when the CPU responds to an interrupt, the IER register of different groups is not cleared by CPU. Can I understand like this? Therefore, for interrupt nesting of different groups, there is no need to enable the IER register within the nested interrupt service routine. However, for interrupt nesting within the same group, the IER register must be enabled, so that the interrupt can be sent to CPU. Can I understand like this?

Thanks very much!

Hi Yun,

I apologize for the delay.

colud you please explain the 4th question in detail? I don't quite understand it.

Please see the 6 Read-Modify-Write Considerations When Using Bit Fields section (specifically 6.1 and 6.1.1) of the C28x Programming Guide linked here for an explanation about this.

And I would like SCIB_RX ISR to be the highest priority, then TIMER0_ISR and EPWM1 last.

In that case, you would need to alter the IER register in all ISRs except the SCIB_RX ISR (top priority) using the masks.

For the sencond question, when the CPU responds to an interrupt, the IER register of different groups is not cleared by CPU. Can I understand like this? Therefore, for interrupt nesting of different groups, there is no need to enable the IER register within the nested interrupt service routine. However, for interrupt nesting within the same group, the IER register must be enabled, so that the interrupt can be sent to CPU. Can I understand like this?

This is correct, in normal operation when an ISR is branched to, the IER bits of other interrupt groups remain enabled. However, if you are trying to do nesting of 3 or more interrupts, you want a prioritization scheme. For example, in your case, you want to:

from SCIB_RX ISR - no nesting

from TIMER0 ISR - enable only SCIB_RX interrupt to nest

from EPWM1 ISR - enable both/either SCIB_RX ISR or TIMER0 ISR to nest

In this case, you want to disable the IER of the EPWM1 ISR inside the TIMER0 ISR to maintain the priority scheme. You are correct about needing to re-enable the IER for nesting within the same group since this is automatically cleared when the ISR is branched to.

Please upvote any responses that were helpful to you

Best Regards,

Delaney