- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software: Code Composer Studio

Hi Vivek,

My custom board encountered the above same situation. I didn't how to deal with. CPU2 cann't run normally. When I program on both CPU with Emulator, CPU2 can't stop at the main() function and without any Hw breakpoints upon finish program the CPU2 flash. It will automatic run, and Stop at the 0x3FE44E。

The program can run well on TI Demo EVM. I didn't make the CPU in the standalone mode but flash mode (IPCbootCPU2 didn't use), just flash mode with emulator,and didn't set any bootctrl register in the program, so bootloader problem may not be involved. Please give some adivce.

For convenience, I open another post as follow:

Thanks!

Hi Chris,

Thanks!

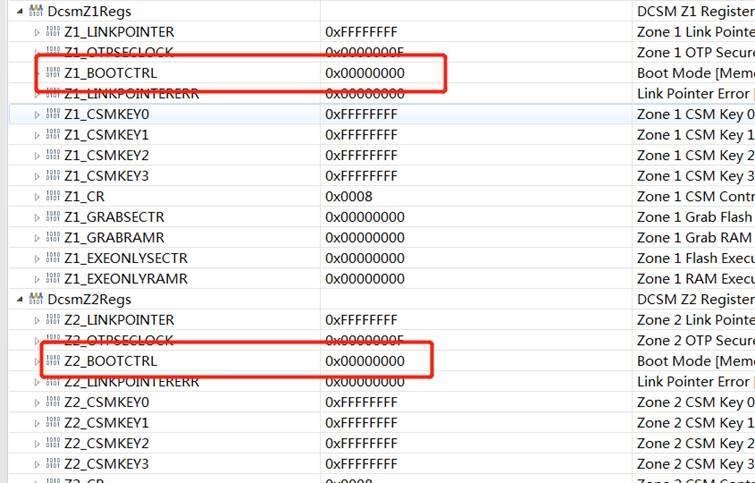

It seems that the initialization value of the Z1_BOOTCTRL and Z2_BOOTCTRL register is abnormal in our custom board, compared with other proper working chips. Since this is a user-configurable DCSM OTP, its default value is set by TI. I didn’t use the On-Chip flash option to erase this register, Because it is very risky, we can only change it once. May waste the chip if it is set incorrectly.

The BootCtrl register of CPU2 in my custom

The BootCtrl register in other working properly board that I have tested display as 0xFFFFFFFF according to the TRM

The default value on the panel of On-chip Flash of CCS is 0xFFFFFFFF, since this register is one time program (OTP) register, I didn’t program the default value now. If it is not planned well, the chip may be wasted! I don't know whether this is the reason that my CPU2 couldn’t work properly.

Could you please give some advice?

Thanks!

Hi,

Yes, Zx_BOOTCTRL location in USER OTP are one time programmable and can not be erased. These are not programmed on fresh part. These are programmed by customers only. Can you check the value in OTP location as well and confirm it's indeed 0x0 ? If yes, then it must have got programmed due to incorrect linker cmd file.

Regards,

Vivek Singh