Other Parts Discussed in Thread: OPA2317, TINA-TI

Hi,

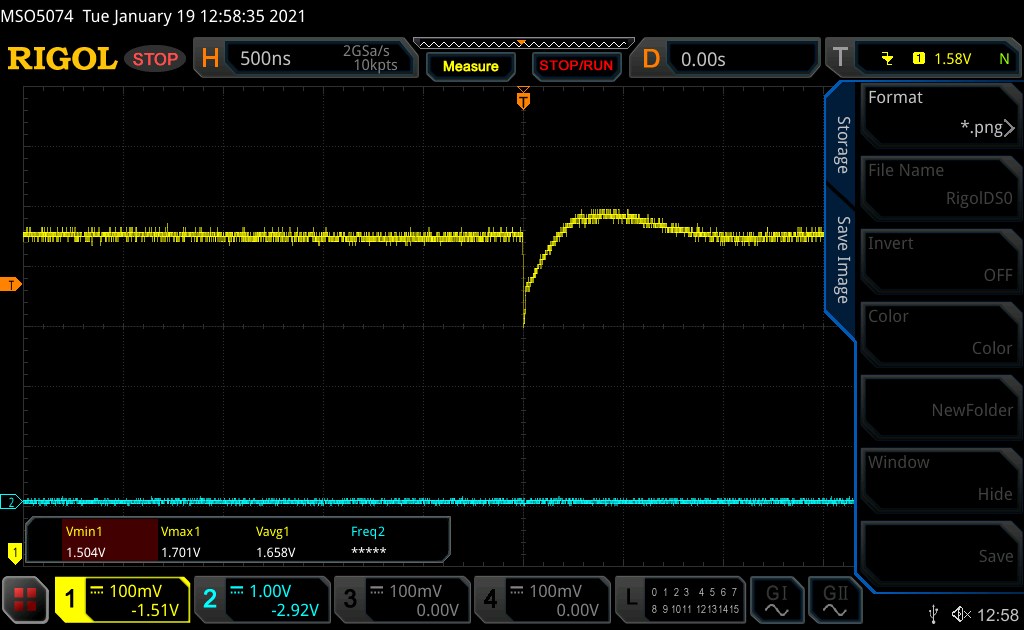

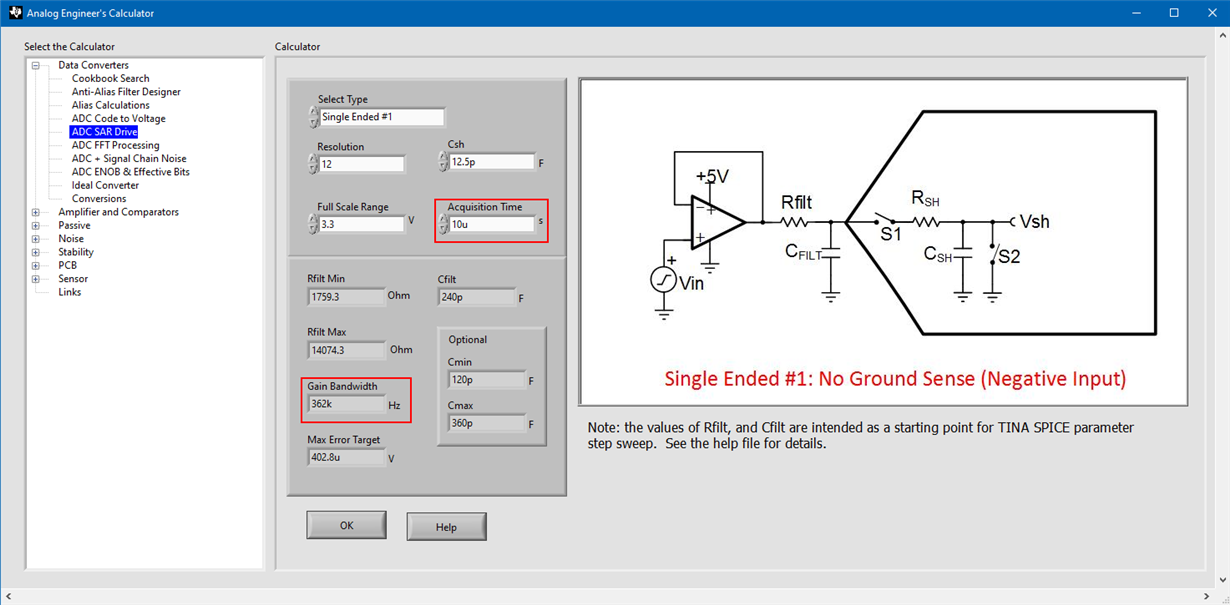

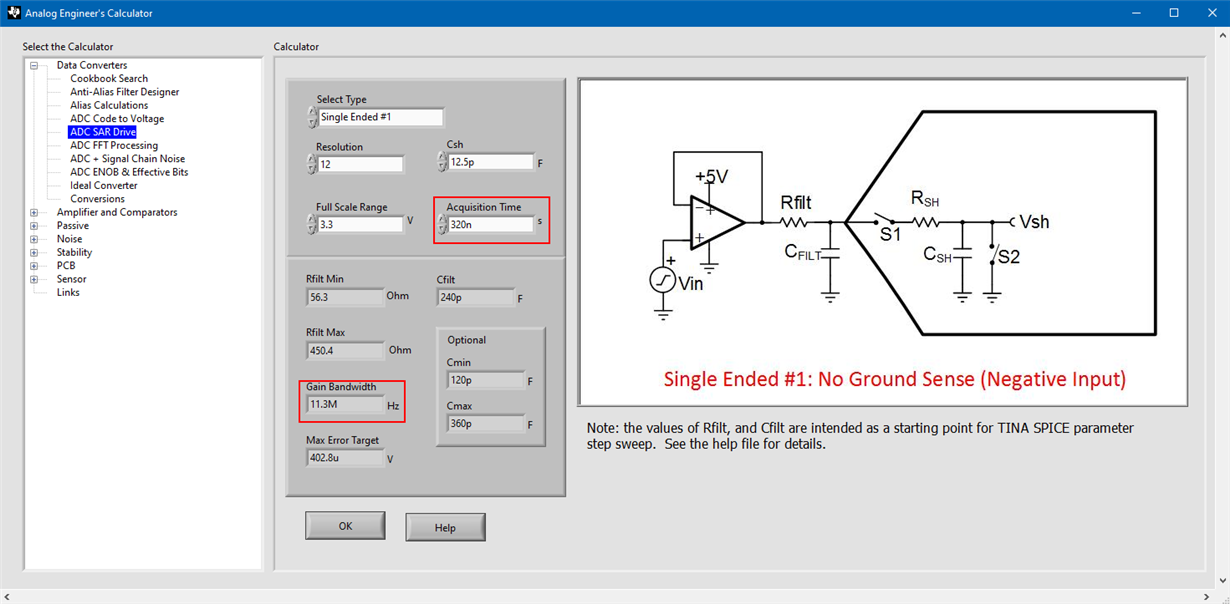

I've 2 signals (Iin_sense and Vin_sense) which have exactly the same analogue circuit driving the ADC. But Vin_sense voltage drops considerably during S/H operation as if large current is drawn while Iin_sense looks perfectly fine. Only difference I can imagine hardware wise is the different ADC input being used. A2/B6 (PIN9) is used for Vin_sense while C0 (PIN12) is being used for Iin_sense. Following are schematics and captured waveform for the Vin_sense signal. As can be seen in the waveform, there is about 160mV of voltage drop during S/H operation. On the ADC data register, I'm measuring 65mV above what I expect to read. I've set ACQPS = 31 and ADC clock equal to 100MHz. All of my other analogue signals are fine as well. It is only the Vin_sense signal which is causing the problem.

Can anyone please provide some insight? Thank you.

Regards,

Muhammad Nouman Sadiq