Other Parts Discussed in Thread: CONTROLSUITE

Hi,

I want to use the F28377 EMIF to control the SDRAM.

Now I want to make sure the whether the hardware configuration is correct.

1.SDRAM selection

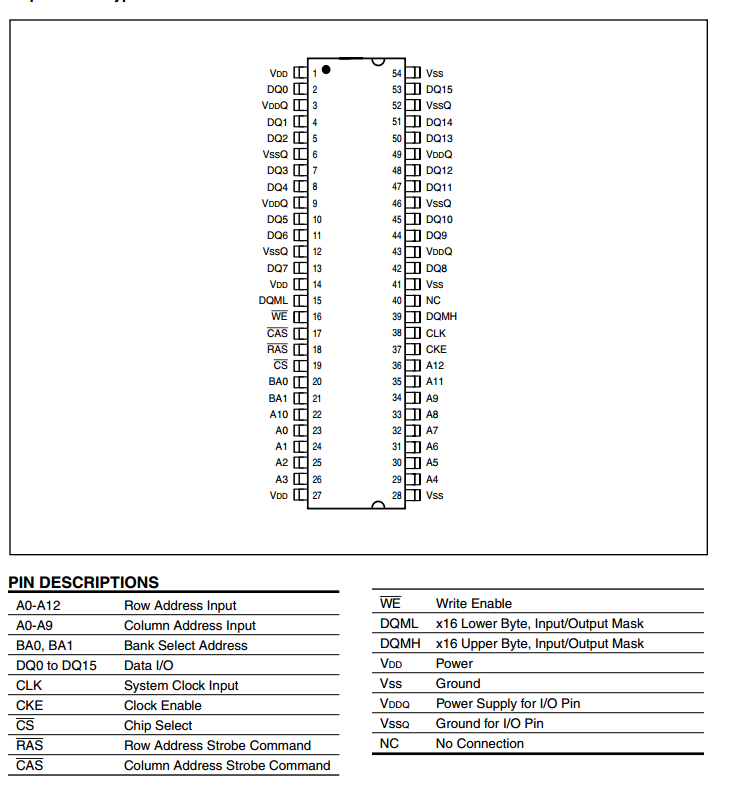

I choose the SDRAM with parameters below as reference.

Type: SDRAM

Data bus width: 16 bit

Supply voltage:3.3V

Organizition: 4/8/16/32M * 16 (I think these are compatible and can be replaced depend on the capacity demand. Is that right? )

But I don't know how to deal with the Maximum Clock Frequency and Access Time.

The Sysclk of F28377D is 200MHz and does it means I must use the SDRAM maximum clock frequency at 200MHz?

And how to choose the SDRAM depend on the Access Time?

I select the SDRAM from MOUSER.

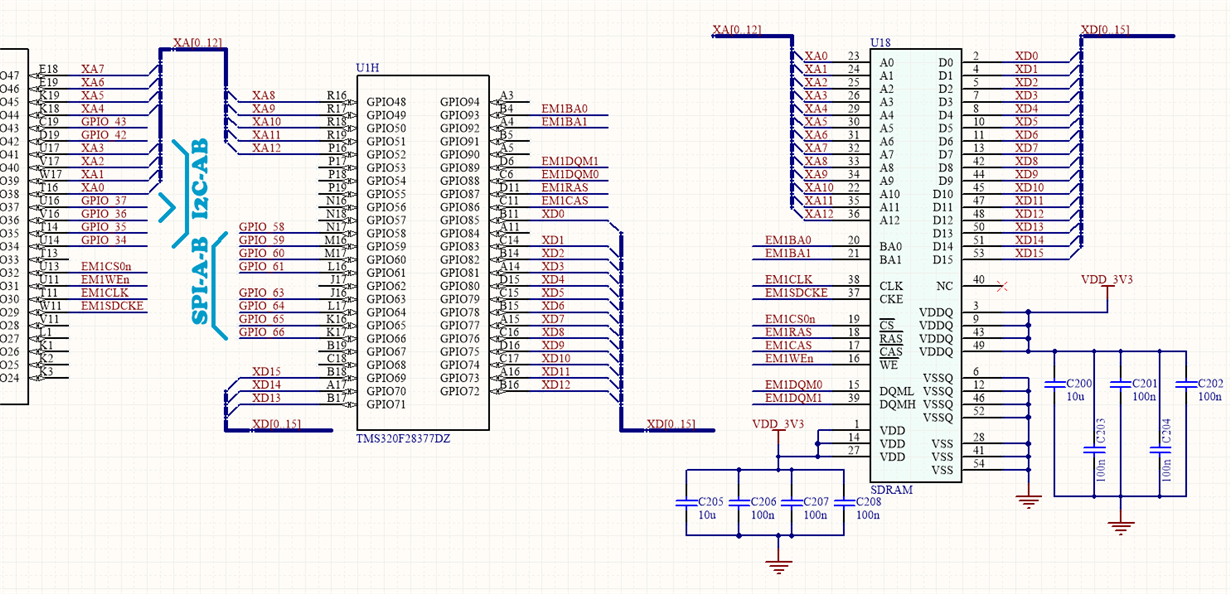

2.Hardware connection

Take the IS42S16320D-7TLI as a example.

I want to know whether the hardware connection is correct.

IO settings:

GPIO 38-41,44-52 as the 13 bit address line;

GPIO 69-83,85 as the 16 bit data line;

GPIO 29 30 31 32 as EMIF SDCKE CLK WE CS0;

GPIO 86 87 AS CAS RAS;

GPIO 88 89 as DQM0 DQM1(DQM0 for DQML x16 Lower Byte, Input/Output Mask, DQM1 for DQMH x16 Upper Byte, Input/Output Mask)

GPIO 92 93 as BA0 BA1;

Is there some examples from TI that show the hardware settings for EMIF to SDRAM?

Looking forward to your reply!

Best regards,

Di