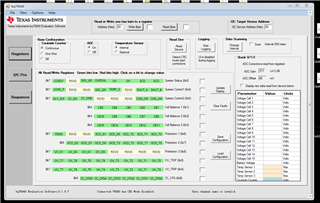

Other Parts Discussed in Thread: BQ76940,

Hi,

I am using 247 to communicate to an I2C device, bq76940. The 247 is unable to talk to the I2C device. I have risen the issue to the bq support group for quite while. This process is resulted in believing the problem is in mastor side of the system. Our design is to use msp430f247 MCU as mastor to communicate to bq76940 as a slave device. The firmware handling the I2C part of code is taking from ti recommanded demo code. Here below is my questions,

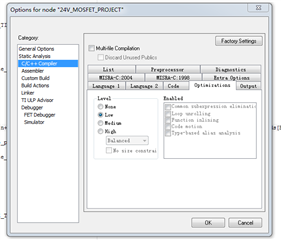

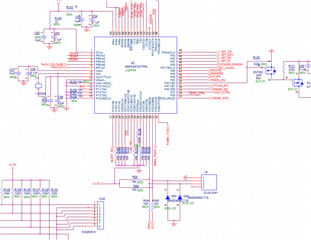

the debug snapshot

The actual code is as follow,

static int8_t I2CSendBytes(uint8_t I2CSlaveAddress, uint8_t *pDataBuffer, uint16_t ByteCount, uint16_t *pSentByte)

{

uint16_t DelayCounter = 0;

uint16_t NumberOfBytesSent = 0;

uint8_t *DataPointer;

UCB0I2CSA = I2CSlaveAddress;

DataPointer = pDataBuffer;

// set to transfer direction, generate start bit

UCB0CTL1 |= UCTR;

UCB0CTL1 |= UCTXSTT;

//waiting for start condition to be generated and slave address to be sent

while (!(IFG2 & UCB0TXIFG))

{

DelayCounter ++;

if (DelayCounter >= DELAY_LIMIT)

break;

}

// if time out for generating start condition, then send stop bit

if (DelayCounter >= DELAY_LIMIT)

{

*pSentByte = NumberOfBytesSent;

UCB0CTL1 |= UCTXSTP;

return -1;

}

// start bit and slave addree have been sent successful,

// so next to send all datas in the data-buffer

for(NumberOfBytesSent = 0; NumberOfBytesSent < ByteCount; NumberOfBytesSent++)

{

UCB0TXBUF= *DataPointer;

DelayCounter = 0;

//check if the byte has been sent

while(DelayCounter < DELAY_LIMIT && (!(IFG2 & UCB0TXIFG) || (UCB0CTL1 & UCTXSTT)))

{

DelayCounter++;

}

//check if NACK condition occurred

if(DelayCounter >= DELAY_LIMIT)

{

*pSentByte = NumberOfBytesSent;

//send stop condition

UCB0CTL1 |= UCTXSTP;

return -1;

}

// here one byte is sent out successfully

DataPointer++;

}

// all datas are sent, clear TX flag, send stop bit

IFG2 &= ~UCB0TXIFG;

UCB0CTL1 |= UCTXSTP;

DelayCounter = 0;

while(DelayCounter < DELAY_LIMIT && ((UCB0CTL1 & UCTXSTP)))

{

DelayCounter++;

}

*pSentByte = NumberOfBytesSent;

//check if NACK condition occurred

if (DelayCounter >= DELAY_LIMIT)

{

UCB0CTL1 |= UCSWRST;

return -1;

}

else

return 0;

}

My question is when execution is stopped at break point, why are the UCTXSTP bit and the UCTXSTT bit already set?

thanks