Hello everyone,

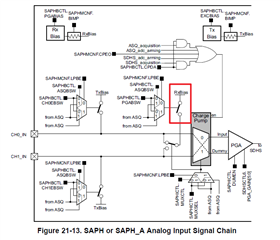

We are looking for some sample code and additional information on how to acquire raw ADC data from the SDHS system of the MSP430FR5043.

i.e. We would like to bypass the USS system control, and simply acquire samples from CH0_IN without any bias directly by the ADC at 8Msps

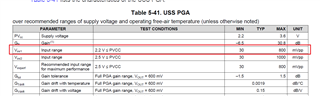

I understand this is possible in "register mode", but it is unclear how to disable the Rx and Tx Bias on the input, and then what the actual input voltage input range will be.

If the bias was disabled, then would the input voltage range be 0 to 1V?

Can CH0_IN be driven directly by an opamp?

Does the CH0_IN always need to be AC coupled due to a limitation in the input structure?

Thanks much for your help and advice.