Hello,

I have a qustion.

My customer want to reduce the active mode power consumption with Captivate.

Then they are considering to reduce MCLK frequency.

What is the possible lowest MCLK frequency for Captivate?

Is there any limitation?

Regards,

Oba

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I have a qustion.

My customer want to reduce the active mode power consumption with Captivate.

Then they are considering to reduce MCLK frequency.

What is the possible lowest MCLK frequency for Captivate?

Is there any limitation?

Regards,

Oba

Hi Oba,

There is no limitation to the Main CLK frequency as it pertains to the captivate module, you can run this as low as the device allows (1MHz). For a process flow if you want to reduce average consumption it does depend on how often the device is awake. I recommend some tests with your application, it could be beneficial to run the MCLK faster so you can get to a sleep mode quicker.

The captivate clock (capclk) won't have the largest change in power and it is recommended to tune this for captivate sensing accuracy opposed to power.

Regards,

Luke

Hello

Is the minimum supported frequency 1MHz?

DCO looks like being set slightly less than 1MHz. And according to the reference manual, DCOCLK can be diveded by DIVM.

So I feel MCLK can be less than 1MHz. No?

Also do you mean lower MCLK( =capclk???) wkill not contribute power consumption?

Because it is 4-20mA sensor side applciation, their concern is not average current but peak current.

Regards,

Oba

Hi Oba,

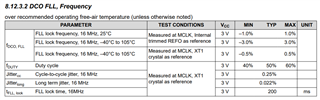

The minimum frequency of the clock generator (DCO) is 1MHz, then the dividers can help reduce the perceived clock value. You are correct the MCLK can run lower, but as it pertains to power the largest bottleneck is the minimum base frequency that the DCO will run before the clock dividers. You will save some power using the dividers but it won't be drastic.

But to fully answer your question, yes MCLK can be less than 1MHz.

The capclk (the captivate module's clock) is a different clock than MCLK and is fixed to 16MHz, I just wanted to avoid any confusion about this.

If they are actively testing this I would check with different settings. Because their concern is peak current then you can lower the DCO to the lowest settings as described in the datasheet.

Regards,

Luke

Hello Luke,

Thanks for your reply.

Regarding the DCO spec, I want to confirm how to understand this speicification.

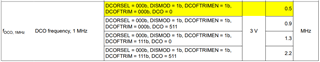

As you mentioned, the datasheet specifies 1MHz DCO range as 0.5MHz ~ 2.2MHz.

But I think this 0.5MHz and 2.2MHz is just a typ value.

What we can guarantee is just that there is an absolutely 1MHz point within this range.

We can't guarantee if there is a point for any other frequnecy like 900KHz and 1.1MHz. (Actually it probably exists)

Is this understanding correct?

I mean around 500KHz can be set probably, but we can't gurantee if 500KHz can be really set.

Regards,

Oba

Hi Oba,

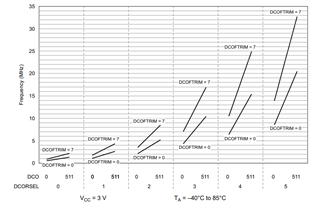

The values listed in the datasheet are typical for the given DCO settings. The graph below shows further detail on the range of specified settings.

The trick here is to use the DCO to help fine tune your clock frequency itself as the value goes from 0 to 511. The typical is also listed because there is the innate accuracy of the DCO itself, which tends to lean ±3% across all temperatures, or ±1% at room temperature.

For DCO power, it will mostly be dominated by the DCORSEL register.

If the 500kHz value would exist, since it is on the edge of the range the lowest value could be 485kHz to 515kHz (this is the ±3%) across temperature. I suggest using the MCLK output to check the exact frequency.

Regards,

Luke

Hello Luke,

Thanks for your reply.

So does it mean the user can set any frequency from 0.5MMHz +3% ~ 2.2MHz-3% if selecting 1MHz range?

Regards,

Oba

Hi Oba,

I wouldn't say "any frequency" as the settings are still limited by the divider options and the DCO so there is a finite amount. But there should be enough flexibility to get close to the user's target frequency.

Regards,

Luke

Hello Luke,

Thanks for your reply.

Is "The deivider options" in your answer FLL?

I missed to think about it.

So the correct explanation is that the user can set any frequency FLL supporting from 0.5MMHz +3% ~ 2.2MHz-3% if selecting 1MHz range.

Correct?

Regards,

Oba

The FLL is the frequency locked loop, which helps stabilize the frequency coming from the DCO output. The dividers are the DCO register that you set specifically, in the graph above you can see it ranges from 0 to 511.

For your user's application I suggest having 1MHz or lower for absolute lowest power, but anything within the 0.5MHz to 2MHz range will have comparable power numbers.

Regards,

Luke

**Attention** This is a public forum