I'm using the watchdog timer and ACLK (standard WDT_ADLY_1000 configuration of the watchdog to provide 1 second interrupts) of this device for simple timekeeping, but I noticed significant deviation from exact time (more or less 3 minutes per day).

Initially I was using a 32.768kHz crystal on XIN XOUT, I changed this crystal for another one, played with load capacitances, but still had this important deviation.I put the fault on the crystal and bought a 25ppm reference clock. So now I feed the XIN with this clock (3.3V, perfect 32768Hz), but I'm still observing the same time deviation.

After quite a lot of investigation, I observed that the ACLK output is not correlated with the XIN signal; in other words it seems that whatever I do, the REF0CLK signal is used as ACLK.

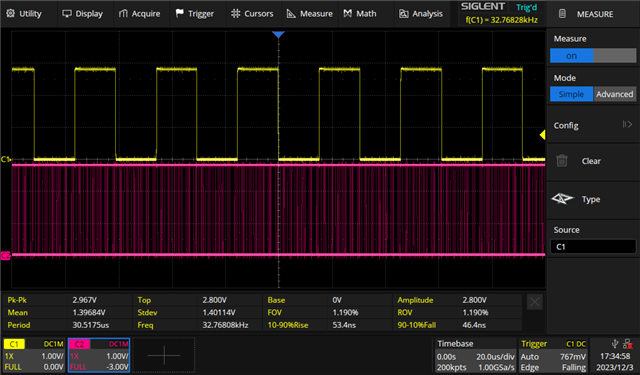

I attached two scope screenshots, the first one synced on XIN input, the second synced on ACLK output.

Of course, I configured USCTL4 with SELA at 0 to select XT1 CLK, and USCTL6 with XT1BYPASS, and confirmed these settings with the debugger.

So, at this point I have no clue on what could be wrong, any help would be greatly appreciated !

XIN Signal (yellow) ACLK (pink), XIN at 32768Hz

l

Same, but synched on ACLK, ACLK is at 32679Hz