Tool/software:

Hi everyone,

I would like to ask/confirm what the ΣΔ ADC input voltages limits are.

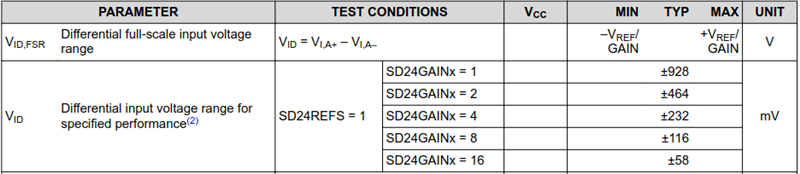

Based on the datasheet, i see that when internal VREF is used (SD24REFS = 1) the differential input range is (as per 8.7.7.4 SD24 Input Range):

When gain is 1x and internal VREF is 1.158V (typical) there is a difference between +/-928mV and +/-VREF.

Is that simply, as the first column suggests, a result of the requirement for performance

Will the performance of the ADC be as stated in the datasheet as long as the input voltage stays within +/-928mV?

My understanding is that when internal VREF is used then FSR is +/-VREF and 0.8*(+/-VREF) when external VREF is used.

In the case of internal VREF, based on the +/-928mV spec, max/min code of the ΣΔ ADC would be ((2^24)/2) +/- ((0.928/VREF) * (2^23)) respectively.

Can you pls confirm?

Regards

Manos Tsachalidis