I need simple code to read and write to I2C devices. The MSP430 is one master and the others are silicon devices.

I find it amazing that you have so many variants of your peripherals that I can not find code that just works without a lot of messaging.

Google searching did not help.

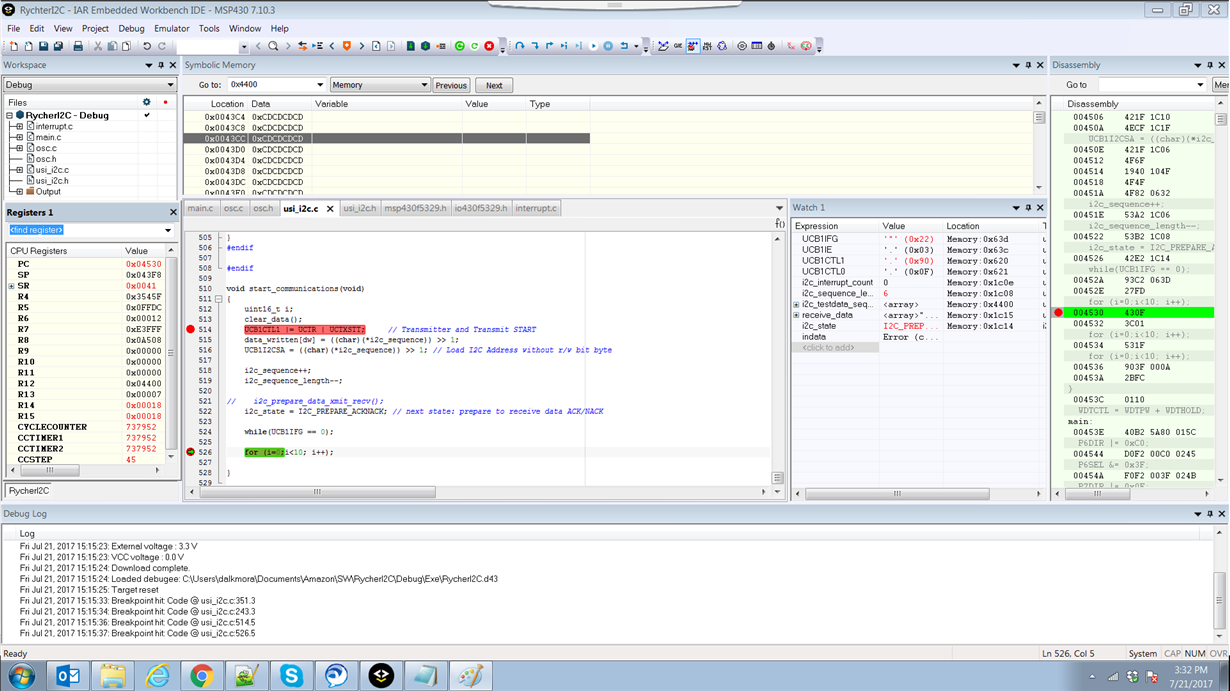

My first thing I found was some code from Jan Richter http://hackaday.com/2014/02/02/a-better-usi-i2c-library-for-the-msp430/

It was written for a different version of the MSP430 but I figured it should be nearly the same right? Wrong. It assumed a USI I2C where the MSP430F5329 used a USCI I2C and they are not alike as I wasted a few days trying to get it to work. It was too different.

Found the MSP430 I2C Wiki http://processors.wiki.ti.com/index.php/MSP430_I2C

It said "Each MSP430 product page has Code Examples .zip file under Software & Tools --> Software"

So I looked there and did find a file that said MSP430F532x Code Examples (Rev. F) (ZIP217KB ) 164views,05 Jun 2017

I thought I was golden until I looked at the code examples for I2C.

Here is the example I2C interrupt routine.

// USCI_B0 Data ISR

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = USCI_B0_VECTOR

__interrupt void USCI_B0_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_B0_VECTOR))) USCI_B0_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCB0IV,12))

{

case 0: break; // Vector 0: No interrupts

case 2: break; // Vector 2: ALIFG

case 4: break; // Vector 4: NACKIFG

case 6: break; // Vector 6: STTIFG

case 8: break; // Vector 8: STPIFG

case 10: // Vector 10: RXIFG

RXData = UCB0RXBUF; // Get RX data

__bic_SR_register_on_exit(LPM0_bits); // Exit active CPU

break;

case 12: break; // Vector 12: TXIFG

default: break;

}

}

Not very helpful, and not what I would call a real example.

I thought I had it with the SLAA382A -- Using the USCI I2C master.

I downloaded the example from SLAA382A which says it is for a USCI I2C Master. But he is using a "MSP430x261x" which uses different pins, different USCI (UCB0 not UCB1), and has separate interrupts for I2C read and write. So it is going to take some work to get to a point to find out where the problems are for my specific device. I already wasted days going down the wrong path.

Why is there not example code for each of your processors? Why so many different I2C peripherals? Get one that works and keep using it. It is not like it is a new interface.

What am I supposed to do? Where do I start?

We are switching from a ST ARM processor to the MSP430 and because we had problems with the I2C on the ST we had to bit-bang the I2C on the ST part. My colleague rewrote the bit-bang code from the ST part to the MSP430 in a day (basically he changed pin names and the timing delay loop), and I can not get it working using the MSP430 I2C peripherals in a week.