Other Parts Discussed in Thread: MSP430F1121A

Hello,

Could you please advise an external circuit that satisfies:

- minimum current consumption for blank part. (The FRAM contents are not programmed after ship from TI.)

- 4-wire JTAG terminals are available for CCS to debug-run.

We would like to be concentrated on the external circuit for 4-wire JTAG pins.

I would think the solution would be a resistor (like 1M_ohms) for each JTAG pins, {TCK,TMS,TDI,TDO}. Do you agree?

Background:

My customer board will be assembled with a battery and spend a pretty long time before programming.

Therefore our point is the power consumption with the blank part.

UG slau445g tells that {TCK,TMS,TDI,TDO} should be opened for 4-wire JTAG. (see 1.6 Connection of Unused Pins.)

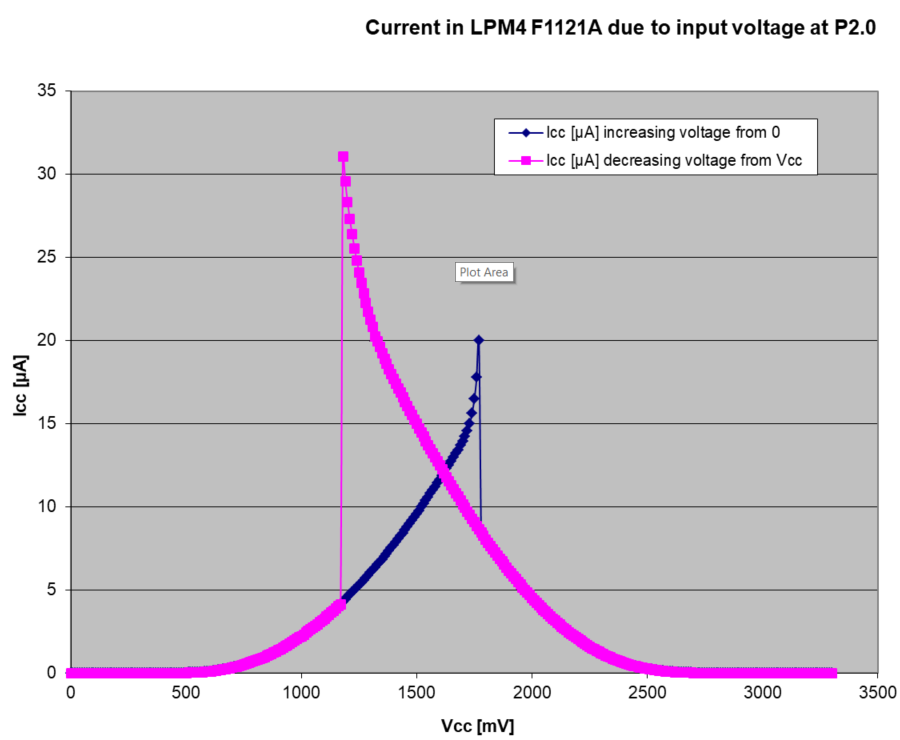

On the other hand, accorgding to customer tests, {TCK,TMS,TDI} needed to be pulled-down to get LPM4 low current.

Then we thought that:

- It would be necessary to pull-up or pull-down JTAG signals {TCK,TMS,TDI} to minimize the current consumption with a blank parts.

- No idea for TDO. Could you please advise also?

- The pull-up/-down resistor value should be larger enough to accept JTAG connections.

Thank you.