Hi

We have an issue in our push-button application where we use the MSP430G2101IPW14. Communication is done over SPI which is very time critical. We have found out that in some push-buttons there is an SPI communication timing issue and the buttons return incorrect data. Our assumption is that the MSP has an issue as we have tried to rule out all other possible error generating factors. The microcontroller is using its internal oscillator.

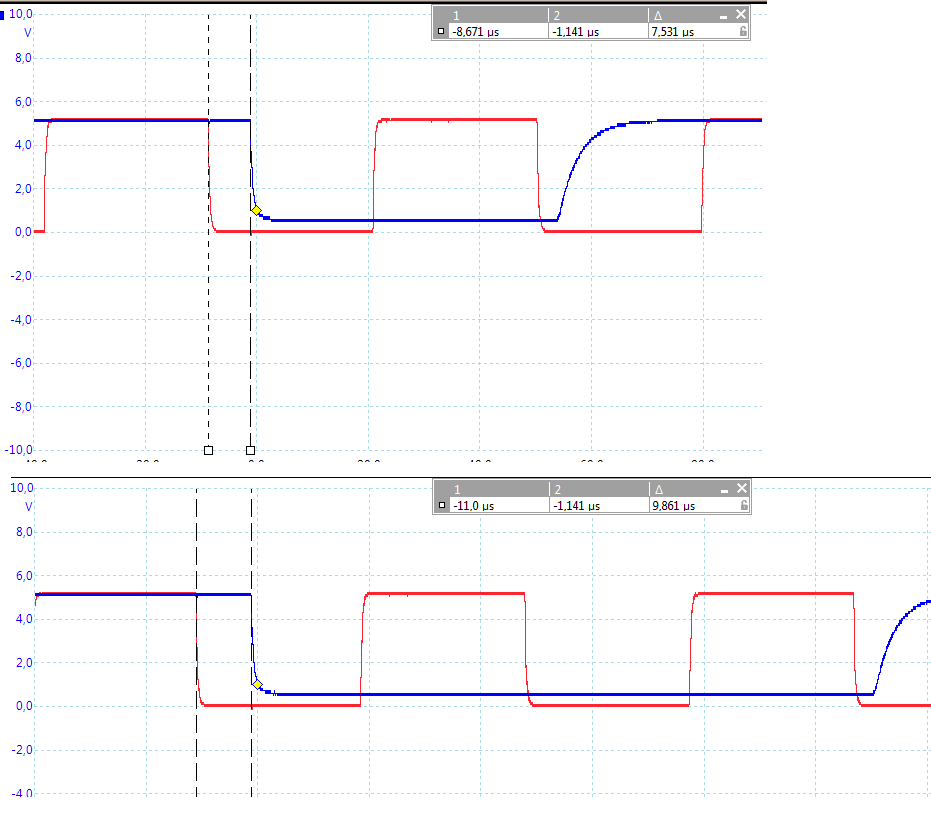

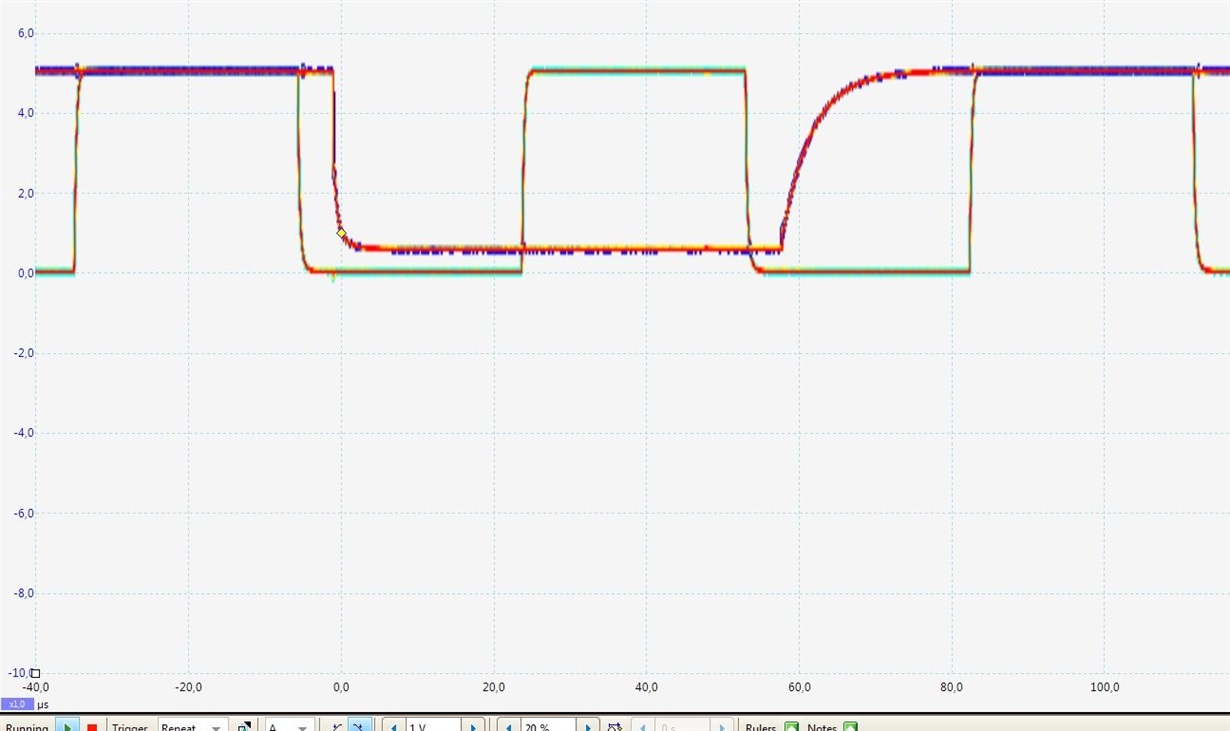

We have tested some fully functional buttons and some failing buttons from our production line. Observations of failing operation can be detected from the attached scope-plots with SPI clock signal on the input and data on the output– there is a noticeable jitter in the failing buttons which causes the problems in our system.

When heating up the MSP with hot air (approx. 100’C) in the failing buttons we have seen that the jitter disappears. We suspect that the problems disappear as the forced heat increases the clock frequency resulting in faster SPI communication and hence the communication delay time decreases.

Please find attached the scope-plots where you can see the SPI clock and the data output signal in the same picture. In a fully functional system, there is no jitter as you can see from the plots, in the other plot there is a 3.3us jitter which causes problems in our production.

Have you seen such behavior in the MSP430G2101IPW14 before? What could possibly be wrong here? Please advice