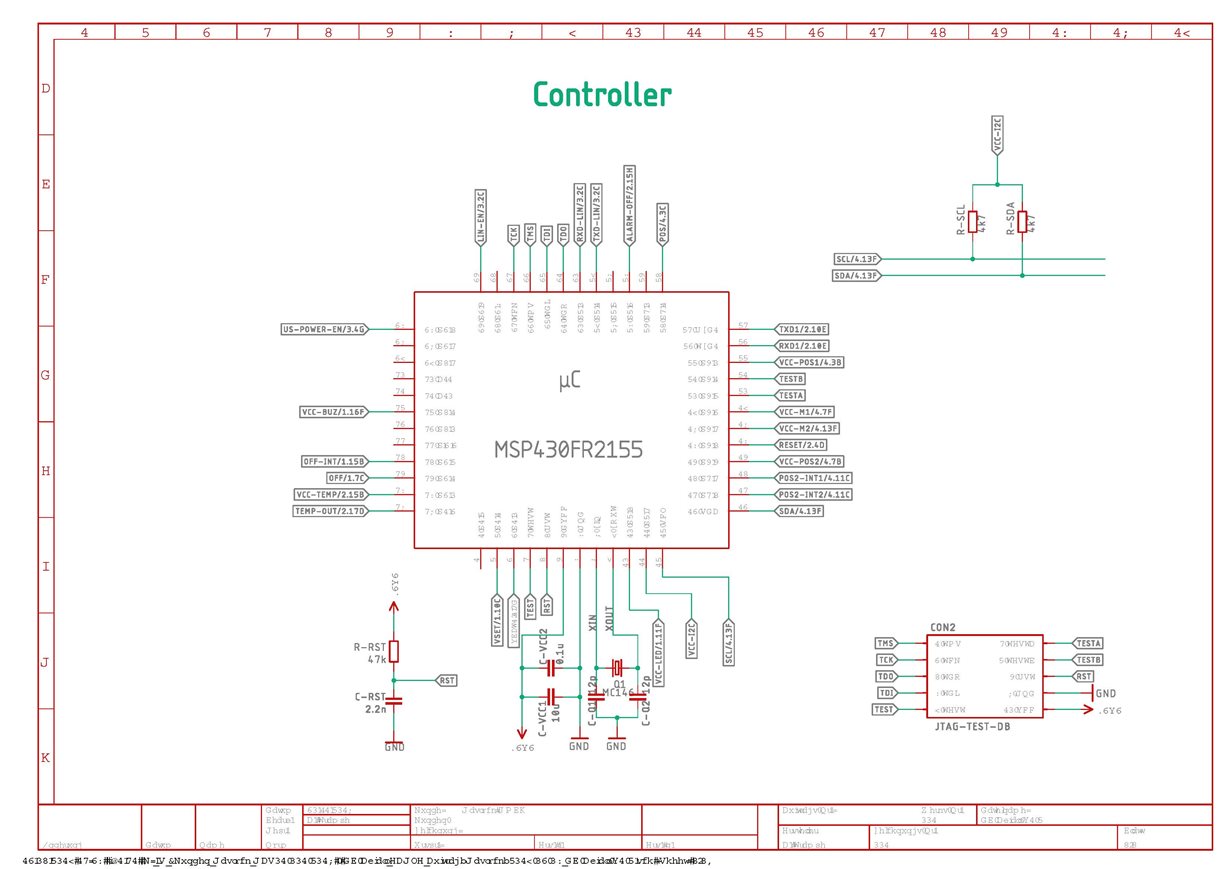

Part Number: MSP430FR2155

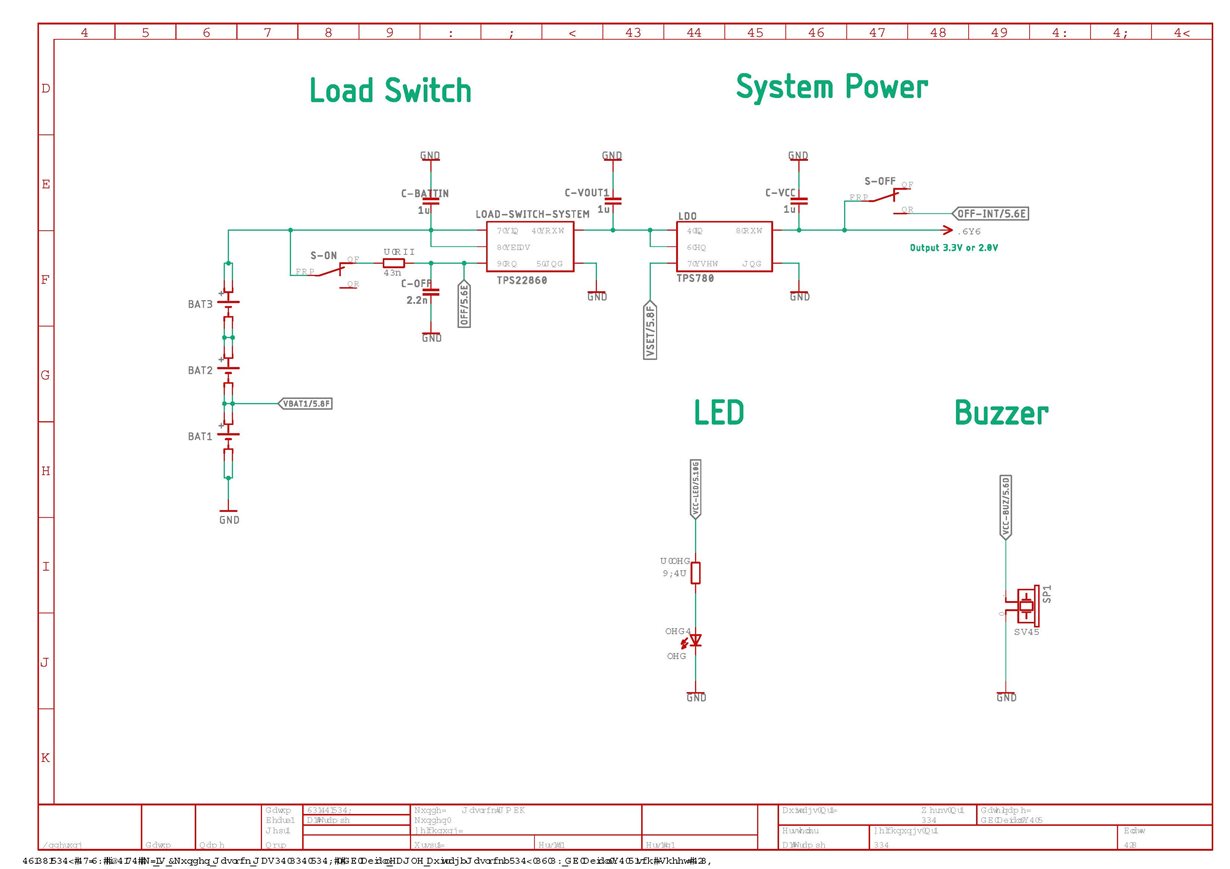

Other Parts Discussed in Thread: MSP430FR2355, TPS22860, TPS780

Tool/software: Code Composer Studio

Hello,

we have a strange problem with I2C bus on our board.

We use among other the components:

MSP430FR2155

On I2C: two EEPROM STM M24512, one Accelerometer Kionix KX122-1037

Pull Up , 4,7kOhm, Pull Up are supplied to the controller, not directly from Vcc,

Bus Capacitance measured on pcb without components SDA to GND 4,1pf, SCL to GND 4,0pF and SDA to SCL 3,5pf

Length of the Wire less then 40mm

We produce 50 boards and on 28 boards, our code stuck with the first I2C Communication. We found that the Controller does not pull down the SDA to GND, no start condition was released.

On some of these boards we remove the Accelerometer and then the code runs.

Then we flashed the sample Code from TI on one of the faulty boards. Also with this code no start condition was released. Both SDA and SCL held on 3.3V.

During debugging we notice, when we set some breakpoints then the code works. At the end, we include a delay loop. With the delay it works, without not.

Do you have any ideas what's could be wrong on the board?

The sample code from TI was slightly modified to set the P2.4 to high for suppling the pull up's and change from Port 0 to 1

* --/COPYRIGHT--*/

//******************************************************************************

// MSP430FR235x Demo - eUSCI_B0 I2C Master TX bytes to Multiple Slaves

//

// Description: This demo connects two MSP430's via the I2C bus.

// The master transmits to 4 different I2C slave addresses 0x0A,0x0B,0x0C&0x0D.

// Each slave address has a specific related data in the array TXData[].

// At the end of four I2C transactions the slave address rolls over and begins

// again at 0x0A.

// ACLK = REFO = 32768Hz, MCLK = SMCLK = default DCO = ~1MHz

// Use with msp430fr235x_uscib0_i2c_16.c

//

// /|\ /|\

// MSP430FR2355 10k 10k MSP430FR2355

// slave | | master

// ----------------- | | -----------------

// | P1.2/UCB0SDA|<-|----|->|P1.2/UCB0SDA |

// | | | | |

// | | | | |

// | P1.3/UCB0SCL|<-|------>|P1.3/UCB0SCL |

// | | | |

//

// Cash Hao

// Texas Instruments Inc.

// November 2016

// Built with IAR Embedded Workbench v6.50.0 & Code Composer Studio v6.2.0

//******************************************************************************

#include <msp430.h>

unsigned char TXData[]= {0xA1,0xB1,0xC1,0xD1}; // Pointer to TX data

unsigned char SlaveAddress[]= {0x0A,0x0B,0x0C,0x0D};

unsigned char TXByteCtr;

unsigned char SlaveFlag = 0;

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

// Configure Pins for I2C

P4SEL0 |= BIT7 | BIT6; // I2C pins

P2SEL0 &= ~BIT4; // I2C Power pins

P2SEL1 &= ~BIT4; // I2C Power pins

P2DIR |= BIT4; // I2C Power pins

P2OUT |= BIT4; // I2C Power pins

// Disable the GPIO power-on default high-impedance mode

// to activate previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

// Configure USCI_B0 for I2C mode

UCB1CTLW0 |= UCSWRST; // put eUSCI_B in reset state

__delay_cycles(50000); // additional Delay

UCB1CTLW0 |= UCMODE_3 | UCMST; // I2C master mode, SMCLK

UCB1BRW = 0x8; // baudrate = SMCLK / 8

UCB1CTLW0 &=~ UCSWRST; // clear reset register

UCB1IE |= UCTXIE0 | UCNACKIE; // transmit and NACK interrupt enable

SlaveFlag =0;

while(1)

{

__delay_cycles(1000); // Delay between transmissions

UCB1I2CSA = SlaveAddress[SlaveFlag]; // configure slave address

TXByteCtr = 1; // Load TX byte counter

while (UCB1CTLW0 & UCTXSTP); // Ensure stop condition got sent

UCB1CTLW0 |= UCTR | UCTXSTT; // I2C TX, start condition

__bis_SR_register(LPM0_bits | GIE); // Enter LPM0 w/ interrupts

// Remain in LPM0 until all data

// is TX'd

// Change Slave address

SlaveFlag++;

if (SlaveFlag>3) // Roll over slave address

{

SlaveFlag =0;

}

}

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector = USCI_B1_VECTOR

__interrupt void USCIB1_ISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(USCI_B1_VECTOR))) USCIB1_ISR (void)

#else

#error Compiler not supported!

#endif

{

switch(__even_in_range(UCB1IV,USCI_I2C_UCBIT9IFG))

{

case USCI_NONE: break; // Vector 0: No interrupts break;

case USCI_I2C_UCALIFG: break;

case USCI_I2C_UCNACKIFG:

UCB1CTL1 |= UCTXSTT; //resend start if NACK

break; // Vector 4: NACKIFG break;

case USCI_I2C_UCSTTIFG: break; // Vector 6: STTIFG break;

case USCI_I2C_UCSTPIFG: break; // Vector 8: STPIFG break;

case USCI_I2C_UCRXIFG3: break; // Vector 10: RXIFG3 break;

case USCI_I2C_UCTXIFG3: break; // Vector 14: TXIFG3 break;

case USCI_I2C_UCRXIFG2: break; // Vector 16: RXIFG2 break;

case USCI_I2C_UCTXIFG2: break; // Vector 18: TXIFG2 break;

case USCI_I2C_UCRXIFG1: break; // Vector 20: RXIFG1 break;

case USCI_I2C_UCTXIFG1: break; // Vector 22: TXIFG1 break;

case USCI_I2C_UCRXIFG0: break; // Vector 24: RXIFG0 break;

case USCI_I2C_UCTXIFG0:

if (TXByteCtr) // Check TX byte counter

{

UCB1TXBUF = TXData[SlaveFlag]; // Load TX buffer

TXByteCtr--; // Decrement TX byte counter

}

else

{

UCB1CTLW0 |= UCTXSTP; // I2C stop condition

UCB1IFG &= ~UCTXIFG; // Clear USCI_B0 TX int flag

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

}

break; // Vector 26: TXIFG0 break;

case USCI_I2C_UCBCNTIFG: break; // Vector 28: BCNTIFG

case USCI_I2C_UCCLTOIFG: break; // Vector 30: clock low timeout

case USCI_I2C_UCBIT9IFG: break; // Vector 32: 9th bit

default: break;

}

}