Other Parts Discussed in Thread: MSP430F6779

Hi,

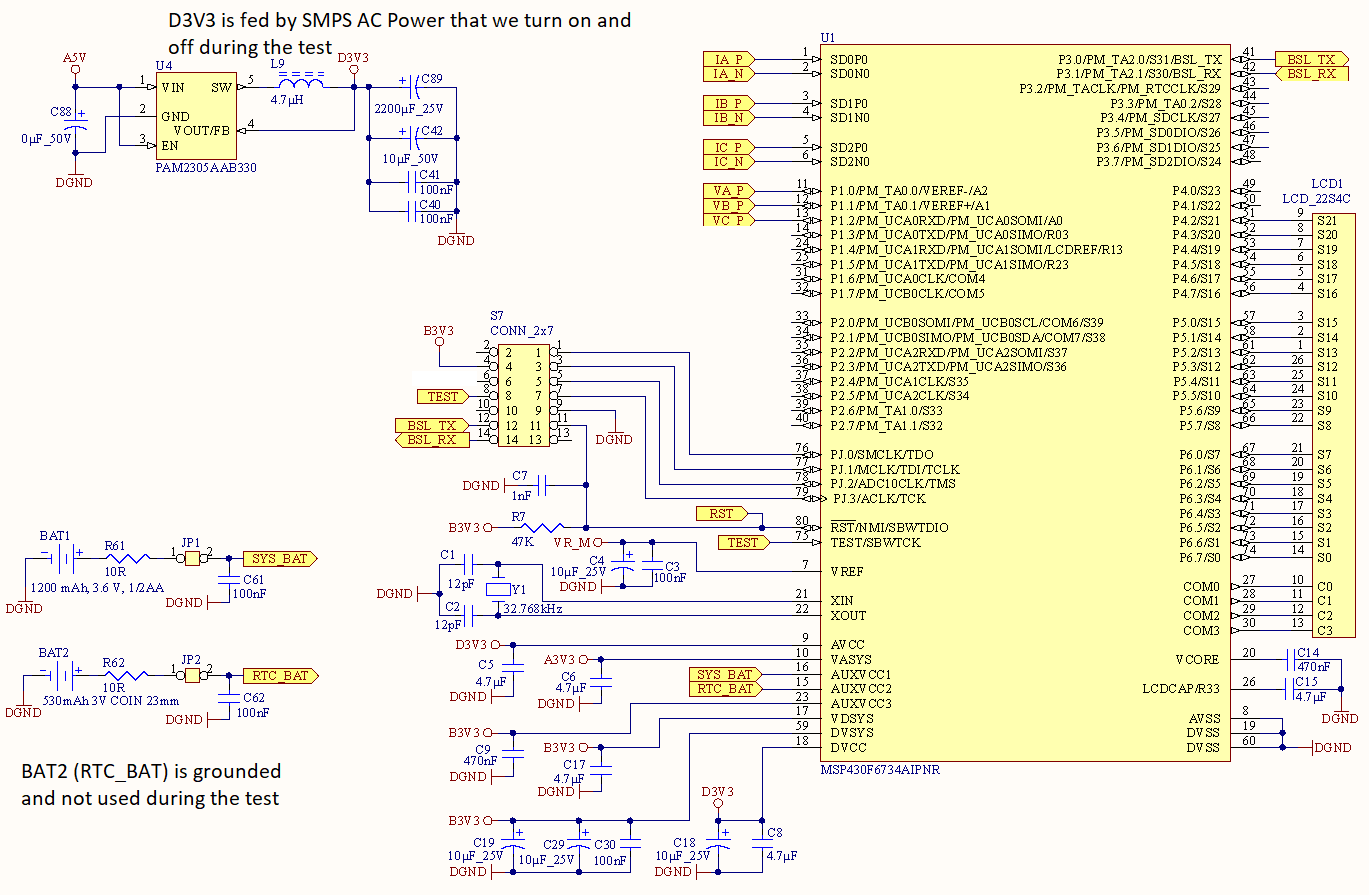

We have a metering application that use one battery and one main power.

VCC = 3.3V comes from AC power.

AUX1VCC = 3.6V battery

AUX2VCC = 0V grounded

AUX3VCC = VDSYS so there will be always power either from VCC or AUX1.

MSP works at 8Mhz with VCore=0 that is 1.35V

My intention is that MSP should enter to LPM3 if we are getting power from battery (AUX1) and wake up if power switches back to AUX0 (that is VCC)

AUX module is configured for fully hardware controlled. There is no software interaction while AUX module does its job.

My configuration below works as expected but sometimes (I hate that word) It doesn't switch to VCC automatically even main power restored.

----

So I studied AUX Module, PMM module and SVS module again in the user manual.

But I didn't understand how exactly they interact each other.

Q1: Do I need to enable SVM (Supply Voltage Monitor) High side in order AUX module to work properly? If yes why and what behavior of AUX module changes if I disable it?

Q2: Will AUX module continue operate in LPM3 mode? Can AUX switch interrupt wake the MCU officially? No one mention this.

Q3: PMM module seems to have a lot of errata. PMM11, PMM15 and PMM26

#pragma vector = AUX_VECTOR /* 0xFFE6 AUX Supply */

__interrupt void AUX_ISR(void)

{

AUXIFG = 0;

LPM3_EXIT;

}

void main(void)

{

// SVS -> Supervisor results in a power - on reset(POR) event

// SVM -> Monitoring results in the generation of an interrupt flag that software may then handle, required by AUX module!!

//

// Low side monitors Vcore

// Highside monitors VCC

SFRIE1 = 0u;

SFRRPCR = SYSNMI | SYSRSTRE | SYSRSTUP; // disable reset pin, ERRATA PMM26: Device lock-up if RST pin pulled low during write to SVSMHCTL or SVSMLCTL

PMMCTL0_H = PMMPW_H;

PMMCTL0_L = PMMCOREV_0; // PMM Core Voltage 0 (1.35V)

SVSMIO = 0u;

PMMIFG = 0u;

PMMRIE = 0u; // ERRATA PMM7: PMMRIE default conditions different than user guide

SVSMHCTL = SVSHE | SVSHRVL_1 | SVSMHACE | SVSMHRRL_1 | SVSHFP | SVMHE | SVMHFP; // that settings for VCC, Warning SVSHFP and SVMHFP bit is added due to PMM15 errata!!

while((PMMIFG & SVSMHDLYIFG) == 0u);

PMMIFG = 0u;

SVSMLCTL = SVSLE | SVSLRVL_0 | SVSMLACE | SVSMLRRL_0; // that settings for Vcore and used in slow performance mode

while((PMMIFG & SVSMLDLYIFG) == 0u);

PMMIFG = 0u;

PMMCTL0_H = 0u; // Lock PMM registers for write access

SFRRPCR &= ~SYSNMI; // enable reset pin

//test = PMM15Check(); this returns 0 as indicated in errata, so we are not affected from PMM15

// Enable control of DVCC, AUXVCC1 but not for AUXVCC2

AUXCTL0 = AUXKEY;

// AUXLVLx = 0 -> 1.67V - 1.74V - 1.80V

// AUXLVLx = 1 -> 1.87V - 1.95V - 2.01V

// AUXLVLx = 7 -> 2.91V - 3.02V - 3.10V

AUXCTL2 = AUXMR_0 | AUX0LVL_7 | AUX1LVL_1 | AUX2LVL_0;

AUXCTL1 = AUX2MD; // AUXVCC2 is software controlled and disabled

AUX2CHCTL = AUXCHKEY;

AUX3CHCTL = AUXCHKEY;

AUXADCCTL = 0u;

AUXIFG = 0u;

AUXIE = 0u;

AUXCTL0_H = 0; // disable

..

..

SET MCLK to 8Mhz

..

..

while(true)

{

// if we are not powered from VCC then enter to LPM3

AUXIFG = 0;

if((AUXCTL1 & AUX0OK) == 0)

{

// wake up when main power back

AUXIE = AUXSWGIE | AUX0SWIE;

// ERRATA PMM11: MCLK comes up fast on exit from LPM3 and LPM4

UCSCTL5 |= DIVM0_L; // MCLK/2=4Mhz

// enter to LPM3

__RESET_WATCHDOG();

__bis_SR_register(LPM3_bits + GIE);

}

// ERRATA PMM11: MCLK comes up fast on exit from LPM3 and LPM4

__delay_cycles(100);

UCSCTL5 &= ~DIVM0_L; // restore MCLK to 8Mhz again

AUXIE = 0;

}

}