I am running Code Composer Studio Version: 10.2.0.00009, simplelink_msp432e4_sdk_4_20_00_12 and testing the adcsinglechannel for TI-RTOS downloaded from your resource explorer.

The default pins for ADC0/1 is PE3/PE2. The test works fine, reporting 0uV and 3300000uV.

But if I move the ADC0/1 to the pins PK0/1 (i.e. ADC ch. > 15) on the header, the test fails reading some 1.5V and sinking slowly while sampling.

I find related issues back in 2019, but I don't expect these problems in 2021.

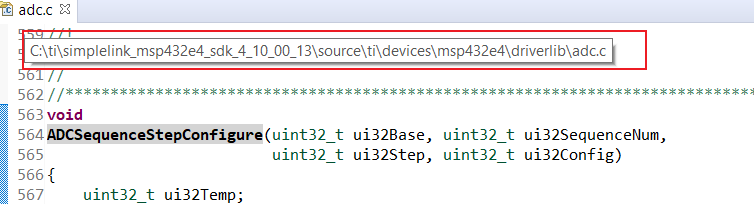

It looks like something is broken in the MAP_ADCSequenceStepConfigure as the bit in the ADC_SSEMUX register is not set for channel numbers >15.

Please advice

Best regards

Terje Froysa