- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear,

Over the last years we have used and designed a board with the DRV8350 gate driver for a light electric vehicle. Right now we are observing our first production series (200 boards, 800 DRV's) with fine results so far.

As we are further developing the system -and spending more time on performance optimization- we are now experiencing two issues with the design involving the DRV8350S gate driver.

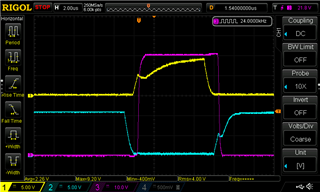

So essentially with low IDRIVE setting we are able to run the board very stable, but in the future we would like to get the mosfets to switch faster to increase performance. We are not sure if the two issues might be related to each other. But the image above shows a clear view of the first issue. (yellow being the high side Vgs, blue low side Vgs, purple Vds low side)

Some background information

Some help would be much appreciated, we have conducted quite some tests already but are not able to find the root cause of the issue our selves.

Kind Regards,

Willem

Hi Willem,

Thanks for sharing results and background information so far.

It looks like the VGS waveform of the high side is charging a capacitive region slowly after the miller plateau is reached, which I agree, it should not turn on like this with respect to source since the dV/dt is much slower than before the miller plateau region.

It may be good to look at the schematic and/or layout as well to see if we can pinpoint any issues.

Thanks,

Aaron

Hi Aaron,

Thank you for your reply. Please find my answers below.

Schematics are mostly according to the TI reference design. Attached a screenshot of one of the gate lines to High Side B. For sharing more details, is a private (e-mail) possible?

We have some bulk caps between DRV and H-bridge due to power routing choices we made.

Cheers,

Willem

Hi Willem,

We have looked into this further and have the following feedback:

Alignment items:

Some thoughts on the debug:

Thanks and Best Regards,

Andrew

Hi Willem,

Following up on this e2e post - please let us know if you need additional support from us on this debug.

Did the information provided below resolve your problem?

Thanks and Best Regards,

Andrew

Hi Andrew,

We have not resolved it yet. Today we did some experiments with different wire lengths/thickness from DRV to mosfets. We are still collecting the data and images and will send you a report later.

Thanks for your patients.

Kind Regards,

Willem

Hi Willem,

Understood, and thanks for the update on this -

To help streamline the scope of the trace thickness aspect of the gate drive trace validation, I would make a quick mention that we recommend 15-20 mils for most applications. Some other top-priority considerations for gate drive traces are:

I've also attached some resource links below, in case your team

https://www.ti.com/lit/an/slva959b/slva959b.pdf (Board Layout)

https://www.ti.com/lit/an/slvaf66/slvaf66.pdf (High-power system design)

Thanks and Best regards,

Andrew

Hi Willem,

Following up on this e2e discussion, do you require any additional assistance on this debug effort?

Best Regards,

Andrew

Hi Andrew,

The issue is still there, we did collect more information and data and will send you an e-mail straight away.

Kind Regards,

Willem Zwetsloot

Hi Willem,

Thanks for the follow-up, and will follow up on this via email. I may need a bit more time than usual to give some more feedback on this, since I have to take care of quite a few lab-related activities due this week

Thanks and Best Regards,

Andrew

Hi Willem,

Sent over some comments via email on the sch/layout documents.

Latest speculation is that the extra 1uF capacitor between VCP pin and GND is not part of the datasheet recommendation, and might explain why VCP/VGLS UVLO errors occur when trying to increase IDRIVE current past a certain threshold. In cases where IDRIVE setting is sufficiently low to not trigger the nFAULT flags, this could still explain the dV/dt being quite low after reaching the miller voltage

Please try depopulating the capacitor, and then let us know if the problem(s) go away

Thanks and Best Regards,

Andrew