Other Parts Discussed in Thread: DRV8706-Q1

Hi, I am working with DRV9706S-Q1EVB and a 5V MCU eval board. Trying to get SPI comms working well.

MCU Eval board SPI and GPIO is at 5V logic level. I have removed all the 0R resistors (R65 to R82) between the onboard micro and the DRV8706S.

I have powered the DVDD pin next to R65 with 5v from the MCU eval board. I have set the nSleep to 5v from the MCU eval board. I can connected Gnd between the 2 eval boards.

I run the SPI at 1000000 baud, CS is active low, clock is idle low, data is read on trailing edge, MSB first.

I find that when reading from IC_CTRL the LOCK bits are not returned as I expected. In D/S it says the LOCK bits shall be 0b011 from reset which is UNLOCK.

I try to write 0b011 to these bits but a further read does not give expected result.

I find when I write to a register I get values returned in the 8 Data bits, although the D/S says it will be NULL values.

Also reading from many other registers the value received does not look correct compared to the expected reset value from D/S.

I have provided PVDD power, but not connected a load or tried to drive any current / PWM out from the Hbridge. I have not tried to set the En_DRV bit in IC_CTRL.

Just trying to read valid values from registers and write some values, for example in DRV_CTRL_1

Is there anything extra I need to know not covered (or seen by me) in the D/S, such as power up sequence, need to have load connected, correct way to use LOCK bits ?

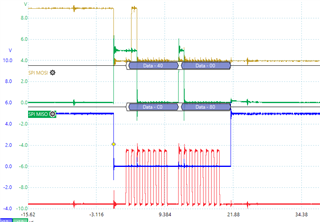

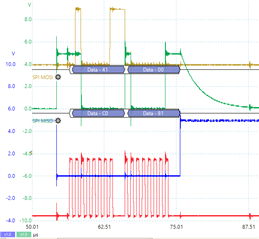

I will attach some images of scope traces. Grateful for any help. All traces are same voltage scaling 5v = 2.5 div

Blue = CS. Red = SCS. Yellow = SDI, Green = SDO

Read IC_STAT_1. Global diag values = 0xC0, data = 0x80 SPI-OK is set

Read VGS_VDS_STAT Global diag values = 0xC0, data = 0x81 SPI-OK is set

Read then write to IC_CTRL.

Lock bits read as 0b010