Good day,

We are developing a light vehicle using the DRV8308. it has performed well so far,except for..

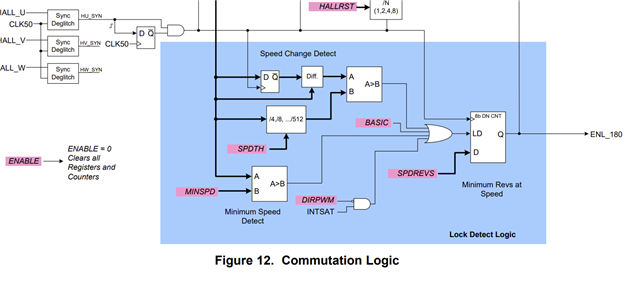

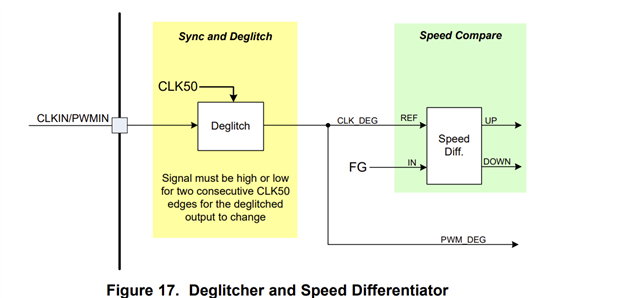

The lock pin, initially I assumed it goes low when the clkin frequency matched the fgout frequency but that doesn't seem to be the case. the functional diagram in datasheet page 23 shows that lock detect doesn't take into account the clkin value at all. The diagram is not really clear, what are the conditions that will lead to the motor controller enabling sinusoidal drive and pulling the lock pin low.

There is a frequency comparison done before the integrator but that doesn't lead to the lock signal logic.

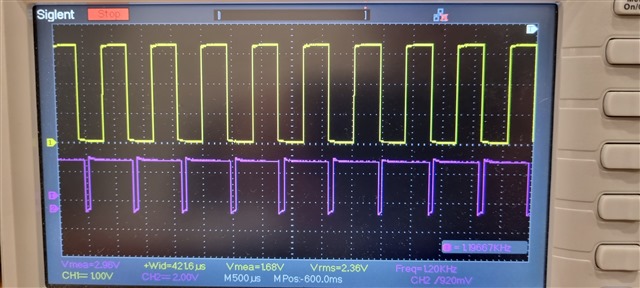

This is a problem for us because we have found a recurring situation where the fgout (motor RPM) is about half the frequency of clkin so the motor is spinning at about half the commanded speed but the DRV8308 has pulled the lock line low.

Our default setting values are:

REGISTER0_SYNRECT (1U)

REGISTER0_PWMF (2U)

REGISTER0_SPDMODE (0U)

REGISTER0_FGSEL (1U)

REGISTER0_BRKMOD (1U)

REGISTER0_RETRY (1U)

REGISTER1_ADVANCE (0x21)

REGISTER2_SPDREVS (100U)

REGISTER2_MINSPD (10U)

REGISTER3_BASIC (0U)

REGISTER3_SPEEDTH (5U)

REGISTER3_MOD120 (3970U)

REGISTER4_HALLRST (0U)

REGISTER4_DELAY (0U)

REGISTER4_AUTOADV (1U)

REGISTER4_AUTOGAIN (1U)

REGISTER4_ENSINE (1U)

REGISTER4_TDRIVE (1U)

REGISTER4_DTIME (5U)

REGISTER4_IDRIVE (7U)

REGISTER5_INTCLK (0U)

REGISTER5_SPDGAIN (2U)

REGISTER6_HALLPOL (0U)

REGISTER6_BYPFILT (0U)

REGISTER6_FILK1 (630U)

REGISTER7_FILK2 (1568U)

REGISTER8_BYPCOMP (1U)

REGISTER8_COMK1 (0x12C)

REGISTER9_AA_SETPT (0x08)

REGISTER9_COMK2 (0x258)

REGISTER10_OCPDEG (3U)

REGISTER10_OCPTH (3U)

REGISTER10_OVTH (1U)

REGISTER10_VREG_EN (1U)

REGISTER10_LOOPGAIN (40U)

REGISTER11_SPEED (600U)

It would be extremely helpful to hear your thoughts

Thanks

Oscar