Hi,

I'm evaluating "DRV8308" now.

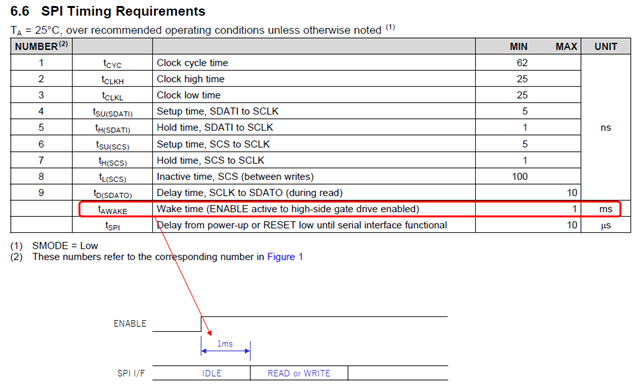

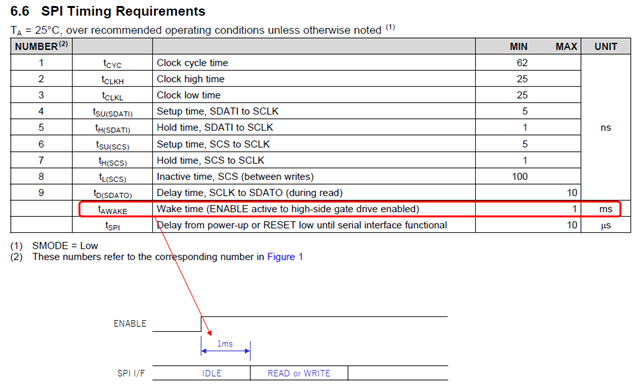

In the attached figure, "tAWAKE" is specified as 1ms (max) as the one of timing requiremet of SPI.

Does this mean that the ENABLE signal must be set to "H"(ENPOL=0) 1ms before the SPI read and write?

Best regards.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I'm evaluating "DRV8308" now.

In the attached figure, "tAWAKE" is specified as 1ms (max) as the one of timing requiremet of SPI.

Does this mean that the ENABLE signal must be set to "H"(ENPOL=0) 1ms before the SPI read and write?

Best regards.

Hi Tokugawa-san,

I believe your interpretation of the datasheet spec should be correct.

Generally speaking, many of our DRV devices have integrated regulators, such as charge-pumps and other LDO regulators.

The reason for that T_AWAKE spec is likely to give the device sufficient time to power up the charge pump, such that the user gives the system adequate time to prepare gate overdrive voltage (VCP) before they start expecting commutation commands to toggle the DRV outputs.

Please let us know if this resolves your question. Thanks!

Best Regards,

Andrew

Andrew-san

Thank you for your reply.

I still have some questions as follows.

1. In case that I activate the Enable and write some register via the SPI, then I inactivate the Enable, does the register value still be retained?

2. When controlling with "Clock Frequency Mode", do I need to activate the ENABLE 1ms before the CLKIN transmission?

3. When I send a reset by the RESET signal, do I need to activate the Enable 1ms before?

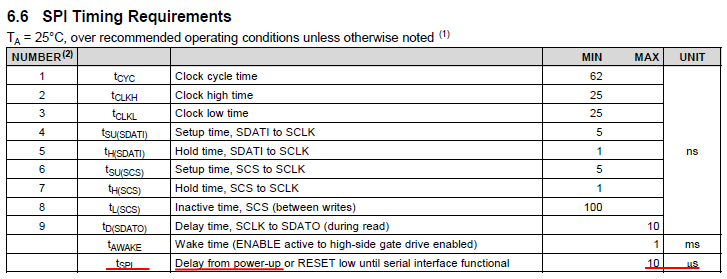

4. "tSPI" is defined in the SPI timing requirements.

It says "Delay from power-up", and I think that the power is naturally turned on at the timing of activating the ENABLE, but I do not know why it is smaller than 10us and 1ms.

Best regards,

Tatsuro

Hi Tokugawa-san,

Some more answers below:

Best Regards,

Andrew

Andrew-san

Thank you for your reply.

I have one more question to ask.

> 3. Datasheet screenshot above will explain the RESET signal operation. Might not need 1ms since RESET pin doesn't involve gate-driver operation.

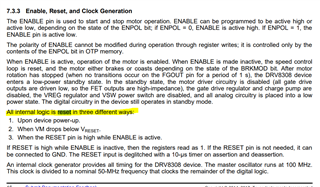

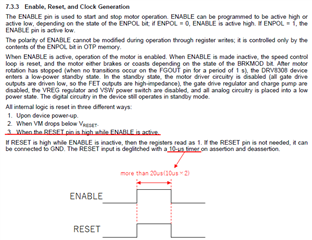

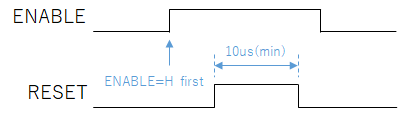

The logic reset is described in the attached diagram as follows:

"3. When the RESET pin is high while ENABLE is active."

Should ENABLE pin be "H(active)" while RESET pin is set to "H"?

Is more than 20us pulse length okay for the RESET and the ENABLE?

Best Regards,

Tatsuro.

Hi Tokugawa-san,

In order for a commanded device-RESET to occur,

Best Regards,

Andrew

Andrew-san

Thank you for your reply.

>3. Deglitch definition

> the RESET pin must remain HIGH after rising edge (assertion) in order for the reset sequence to proceed

> the RESET pin must remain LOW after falling edge (de-assertion) in order for reset sequence to end

That mean more than "10us" pulse length is okay for the RESET?

Best Regards,

Tatsuro.

Hi Tokugawa-san,

That explanation looks correct, and your diagram explains it well.

Yes, more than 10us of pulse length is actually required* in order for the RESET to process, and this is called 'deglitch' time.

The purpose of deglitch in this case is to ensure that brief noisy transients on RESET pin (<10us) don't cause the device to RESET accidentally

Best Regards,

Andrew