Other Parts Discussed in Thread: DRV8830, DRV8832,

Hello,

In a previous post there was mention that

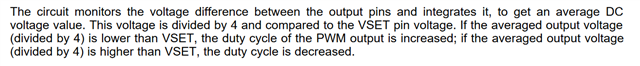

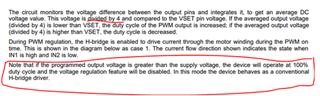

>VSET can be adjusted while the motor is running, but there will be some delay before the motor meets the new target voltage due to the integrator shown in the functional block diagram.

I am interested in using this for a robotics platform that will have an inverted pendulum task (2-wheeled balancer) and worried about any added delay. How much delay are we talking here? Microseconds? Milliseconds? Seconds?

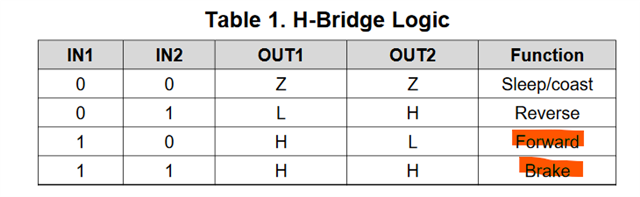

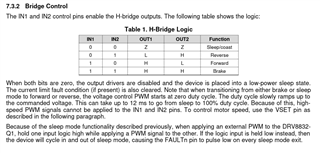

Also I am curious about how the forums and how the datasheet are specifying to control the motor speed. According to the datasheet (Section 7.3.2):

It says we should "hold one input logic high while applying a PWM signal to the other. If the logic input is held low instead, then the device will cycle in and out of sleep mode, causing the FAULTn pin to pulse low on every sleep mode exit." Wouldn't this cause the times where the PWM is low to Brake the wheel as opposed to coasting? This seems like it would generate a bunch of near-stall current. Can someone clarify if this is correct and if so, why this wouldn't cause near stall currents to be induced with each PWM cycle? If this is wrong, and we are supposed to be holding the logic input low, then how do we avoid this FAULTn?

Best regards,

Christopher