Hello Team,

I have some doubts related to the Phase comparator unit in DRV3256-Q1

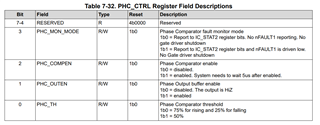

Q1 -- As per the PHC_CTRL Register Field Descriptions,

When the PHC_TH is set to 1b0 = 75% for rising and 25% for falling , does this mean that the mis-compare will be reflected on PHC pin only when transition is happening (either falling edge or rising edge); or will it be also reflected when the SHx is at some fixed voltage level (for e.g. say 15% of DHCP).

Q2 -- Would be useful if you help me with the response of the PHCx pins as per below table

| PHC_TH | Voltage at SHx | PHCx PIN STATE |

| 1b0= 75% for rising and 25% for falling | Above 75% of DHCP | |

| Below 25% of DHCP | ||

| Between above range | ||

| 1b1 = 50% | Above 50% of DHCP | |

| Below 50% of DHCP |

Thank you.