Hello,

My customer is wondering how accurate the VREF voltage is inside the DRV8889-Q1. Would you please tell me the ADC bit number used for VREF?

Best Regards,

Yoshikazu Kawasaki

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

My customer is wondering how accurate the VREF voltage is inside the DRV8889-Q1. Would you please tell me the ADC bit number used for VREF?

Best Regards,

Yoshikazu Kawasaki

Hello Kawasaki-san,

VREF is externally input to the DRV8889-Q1 VREF pin. The accuracy of the VREF voltage depends on the external source. If can be sourced from DVDD, DVDD min-max specification is in the datasheet.

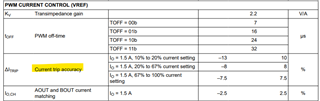

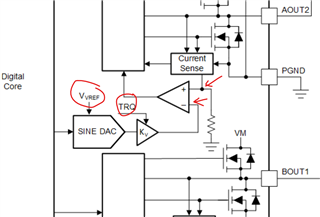

Current regulation is done by analog circuitry using a ITRIP comparator. The accuracy of current regulation over the current range is provided in the datasheet.

Regards, Murugavel

Hello Murugavel-san,

Thank you very much for your quick reply.

I wasn't understandable enough for you, so please let me ask you differently.

We know VREF is an input pin from an external source. What we don't know is how VREF is dealt with internally. VREF is used to calculate the full-scale current with TRQ_DAC as shown on page 20, so we think it will be converted to digital by ADC internally and would like to know the bit number if our understanding is correct. Would you please tell me that? I hope my question is understandable for you this time.

Best Regards,

Yoshikazu Kawasaki

Hello Kawasaki-san,

See below block diagram snippet from the datasheet. The TRQ_DAC controls Kv gain parameter to scale the current. It is a 4-bit DAC based current scalar as mentioned in the page-20 of the datasheet. The SINE DAC is used for microstepping. VREF is not converted to digital by ADC internally. The ITRIP comparator shown in the diagram generates the tON and tOFF except for STRC decay mode where tOFF is not fixed, it is determined by current ripple settings. I hope this helps. Thanks.

Regards, Murugavel

Hello Murugavel-san,

Thank you very much for your quick reply again.

We basically understood how VREF is used internally, but do you have materials showing how SINE DAC and Kv blocks work for non NDA customers?

Best Regards,

Yoshikazu Kawasaki

Hello Kawasaki-san,

What we have in the datasheet is what we have for non-NDA and NDA customers. At a high level, the SINE DAC generates a sine table based analog voltage levels required for microstepping of each quadrant (one quadrant repeated 4-times to cover the four quadrants) which scales the KV in the analog domain as per the required current levels.

Likewise TRQ_DAC also scales the KV in the analog domain exactly as shown in the high level block diagram in the datasheet.

Is there a specific concern the customer has currently with this? We can try to address it if we know the specifics. Thanks.

Regards, Murugavel

Hello Murugavel-san,

Thank you very much for your comments again. I asked the background of the questions from my customer. They'd like to make sure how accurate the IFS would be. They understand it is defined by the equation(1) shown on page 20 which has 2 parameters, VREF and TRQ_DAC. However they think TRQ_DAC is coarse since it has only 4 bits. Therefore they think they should fix TRQ_DAC=0000b and control VREF to have fine value for full scale. That's why they're asking VREF. Do you also think they should control full scale current by VREF if they need fine full scale current?

Best Regards,

Yoshikazu Kawasaki

Hello Kawasaki-san,

Thank you for following up with the customer.

You mentioned, "However they think TRQ_DAC is coarse since it has only 4 bits. Therefore they think they should fix TRQ_DAC=0000b and control VREF to have fine value for full scale. That's why they're asking VREF. Do you also think they should control full scale current by VREF if they need fine full scale current?". Yes this is the best way to set the IFS for Run current with TRQ_DAC then customer can use TRQ_DAC to reduce the hold current when the stepper is in stop but bridge enabled for desired hold torque. This will reduce power dissipation in the motor. Before applying step pulses customer can set the TRQ_DAC to 100%.

Regards, Murugavel