Other Parts Discussed in Thread: DRV8316,

Hi Team,

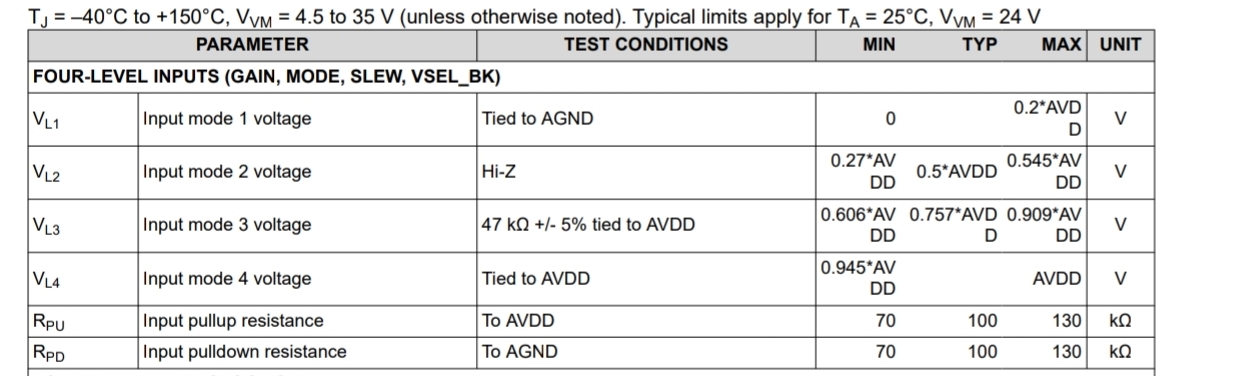

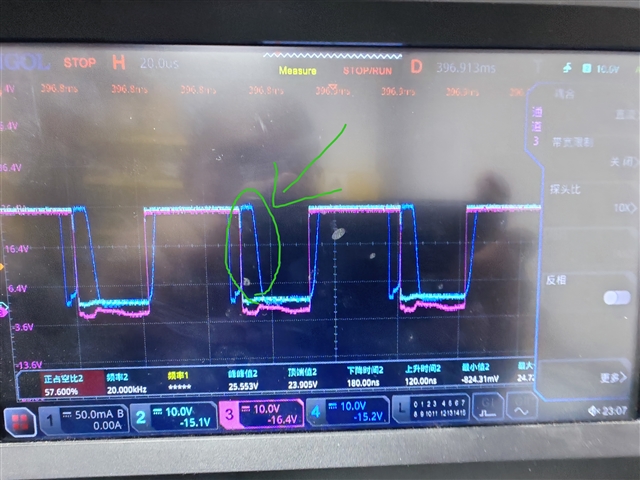

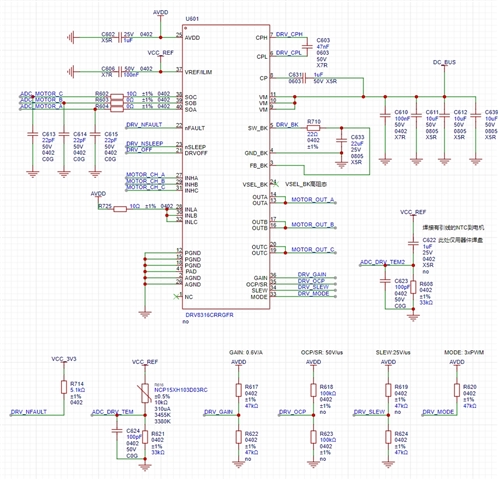

After DRV8316CT-Q1 is powered on, AVDD can output 3.3V normally, but the configuration pins GAIN/MODE/OCP/SLEW are not pulled up. If the pull-down resistor is not attached, it will be around 0.2V. If only 47KΩ pull-up is attached, the voltage will be 3.3V. If only 47KΩ pull-down is attached, the voltage will be 0V, and the remaining pin configurations will be normal.

Pin configuration diagram:

Regards,

Annie