Hello TI

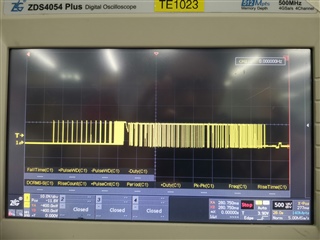

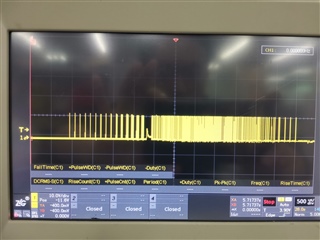

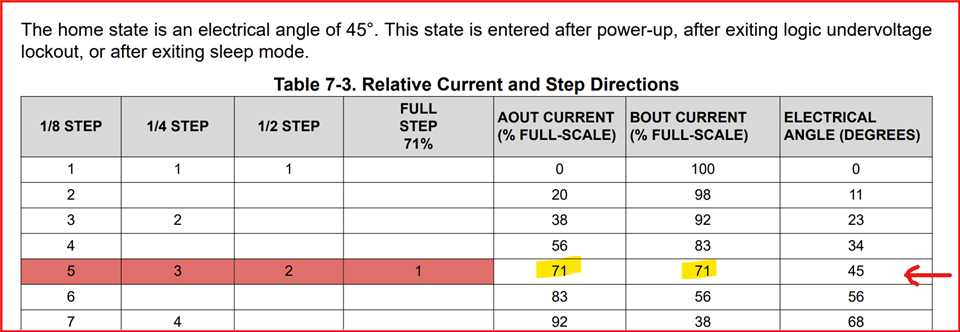

When I use the same configuration input to DRV8889-Q1, including SPI register configuration, VREF (35%), STEP transmit frequency configuration, etc.

There will be a very noisy motor caused by the first movement of the motor after the first power up of the software outputting 2.5 times more current.

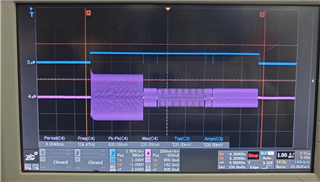

In the figure below, there are five movements, and the VREF (blue line) input is the same throughout the whole process. The amplitude of AOUT1 in the first movement is nearly twice as much as in the second movement, but the frequency of the first movement, the second movement, and the last movement are the same.