- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Hi team,

When we tested the VDS overcurrent fault of DRV8703, we had the following two questions:

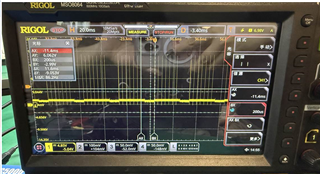

1. After the overcurrent fault occurs, the T retry time is 3ms, but in the actual test, after the error is reported 7 times, there will be an interval of 11ms. Is this normal?

2. Why is the error fault bit not latched when an overcurrent fault is reported?

(Each spike in the figure represents the re-driving action of DRV8703 after an over-current fault occurs)

BR,

Ethan

Hi

Thank you for your questions. Will review it and feedback to you in a day or two.

Hi Shinya,

Okay, I will loop you in customer's email, so that we can talk more directly with customer, thanks!

MAA is Shanghai Qiangu, Project is Braking (EHB) for SGMW

BR,

Ethan

Hi Eathan

Here is feedback.

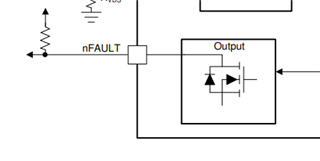

1) In order to confirm retry period, need to measure nFault signal. Then it could be ~3ms. Customer should have pull up resister (e.g 5Kohm to 5V) externally.

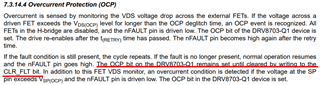

2) OCP fault bit is cleared by writing CLR_FLT bit. Not cleared by retry.

regards

Shinya