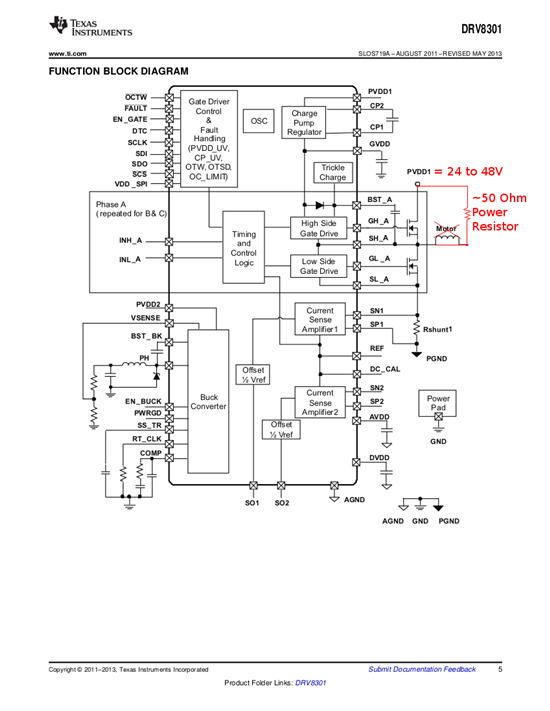

I'm using the DRV8301 to drive a two-phase buck-converter to charge a 24V battery. In this situation, the half-bridge outputs have a non-zero voltage (about 24V) present on them before the DRV8301 starts driving the FET gates.

The presence of 24V almost guarantees that the output bootstrap capacitors will start with no charge. If the half-bridge output is 24V, the BST_x pins will have higher voltage on them than the GVDD voltage of ~10V. I believe this causes a small reverse leakage current through the internal bootstrap diode which discharges the bootstrap capacitor to have zero or slightly negative voltage.

At first I hoped the DRV8301 trickle charge circuitry would counteract any leakage on the bootstrap capacitor. However, the trickle charge circuitry only seems to operate when the INH_x input is high. This makes sense, since the datasheet only specifies the trickle charge circuitry allows 100% duty operation, not that it pre-charges the bootstrap cap:

"Bootstraps are used in highside FETs of three-phase pre-gate driver. Trickle charge circuitry is used to replenish current leakage from bootstrap cap and support 100% duty cycle operation."

It would be nice if the trickle charging was operating all the time and the bootstrap cap would automatically be charged a few milliseconds DRV8301 gate enable signal was asserted.

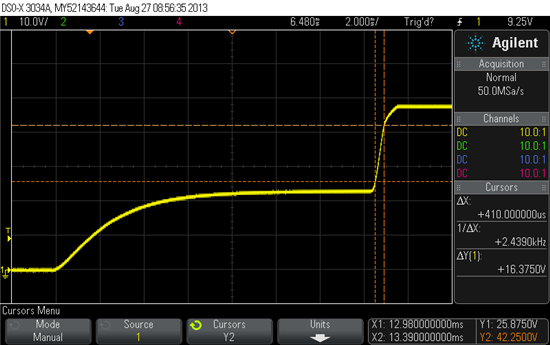

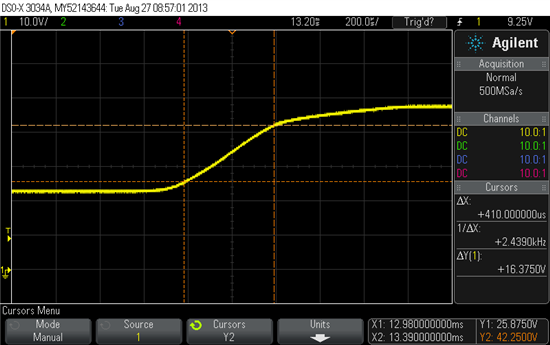

With most bootstrap-based gate drivers without trickle charging, you need to pulse the lowside FET on for a few short bursts before enabling the normal PWM operation. These short on pulses on the lowside FET will drive output voltage to zero and charge the bootstrap capacitor through the bootstrap diode. The short pulses also slowly pump up the bootstrap capacitor instead bringing it to full voltage all at once.

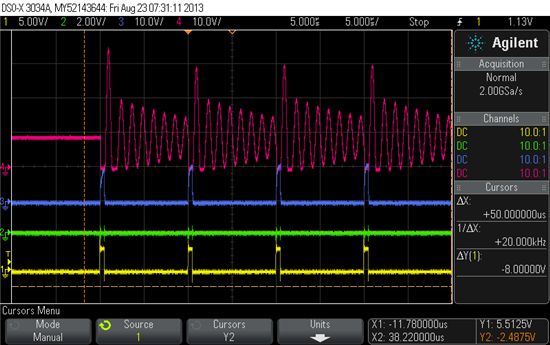

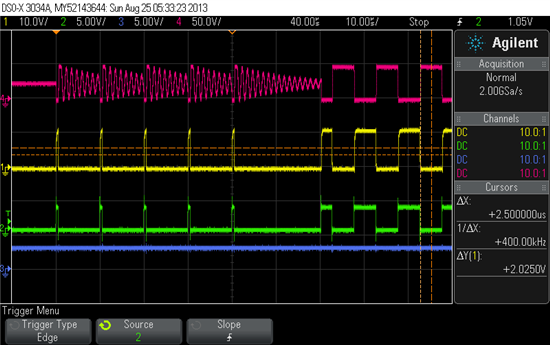

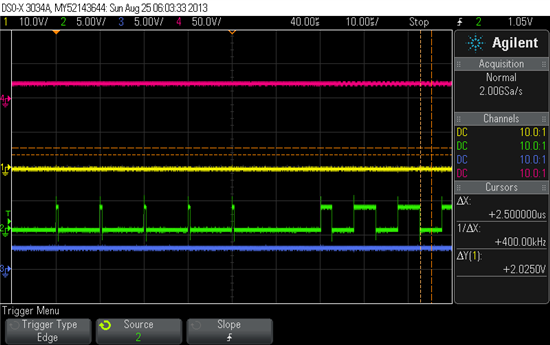

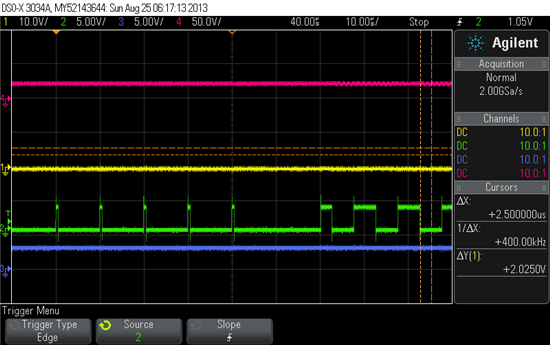

In my case the short pumping pulses work... but only sometimes. Much of the time, the DRV8301 totally ignores the low-side gate pulse (the input get the signal, but the LS gate output does not do anything). When the lowside gate pulse is ignored, it is always ignored, no mater how long it is run. This is not caused by a FAULT or OCTW. I tie both signals together and never not see it assert low when DRV8301 is ignoring low-side pulses. However, I do get a OC fault on the high-side FET the first time the highside input is asserted. I believe this is because there is no voltage on the bootstrap capacitor and no voltage voltage to HS FET Vgs. The FET is not turned on and the OC detects this as a high-side MOSFET is over current.

When the DRV8301 does let the low side pulses through, it does so immediately. I've never see it drop the first few drop the first few pulses and then start working later. However, when the pulses do go through, they usually work again if I reset the DRV8301 and restart soon after.

I have the software write and verify the DRV8301 control registers before sending the first PWM signal, so I'm sure the DRV8301 is powered-up and operating. I also poll the GVDD_UV status bit through the SPI, so I know the GVDD is happy before starting up. I've also tried a different board so it is unlikely that the problem is caused by a damaged DRV8301.

If I don't have an external 24V on the half-bridge before starting, the low-side pulses always go through without issue. However, there will always be an external 24V on the half-bridge outputs in the real system, so this is not a fix.

I'm guessing there is something wrong with the handshaking between the lowside and highside signals when there is no voltage on the bootstrap cap. Is it possible to get a description on how the handshaking operates, or a confirmation that this might be an issue?

I would also appreciate any suggestions on how to trick the trickle charge circuitry into the pre-charging the bootstrap capacitor. I am considering putting the DRV8301 in OC protect mode, pulsing the high-side PWM, and then waiting for OCTW/FAULT to stop occurring before switching to a full PWM. This is an ugly hack, but might work.