Hello,

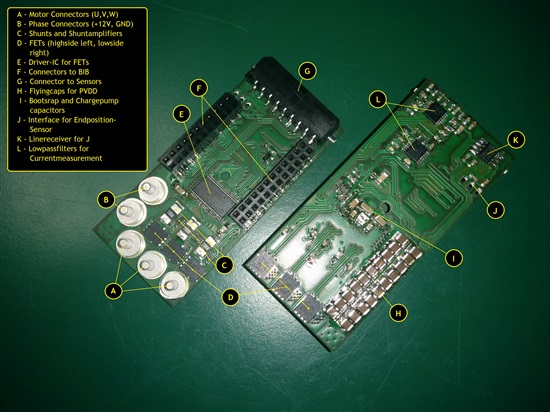

for my thesis i'm working on a BLDC driver for sine-commutation that can drive up to 1kW in a tight package using the DRV8303 in a 12-15V net (Automotive). The whole board is about the size of a Creditcard (Mikrocontroller is extra). The first iterarion (not packed very tight) worked quite good, but now i downsized the whole thing. It is now a high-build board, i added 3 highside-shunts R001 with INA213 amps at 2.5V reference(TLV2771) with 4th deg. FIlters (TLV2774) and changed the FETs to CSD18532Q5B.

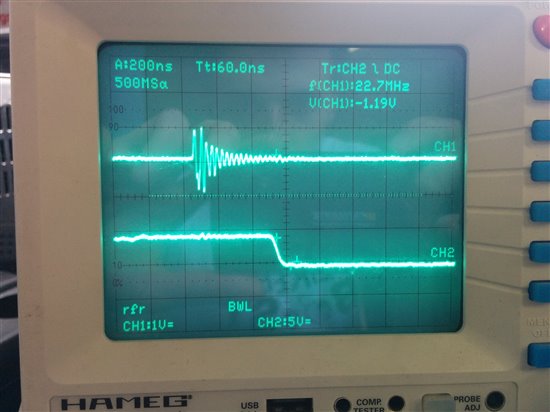

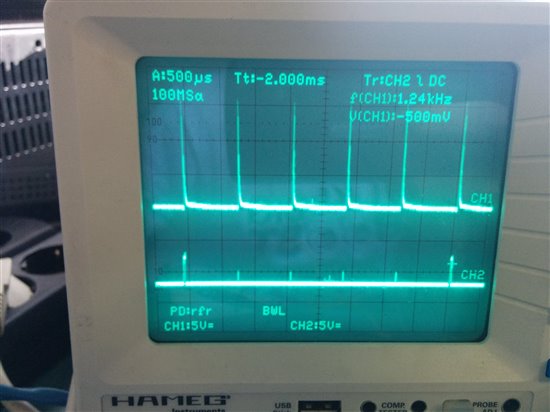

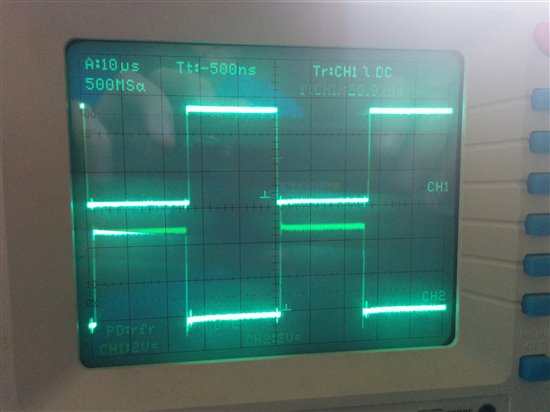

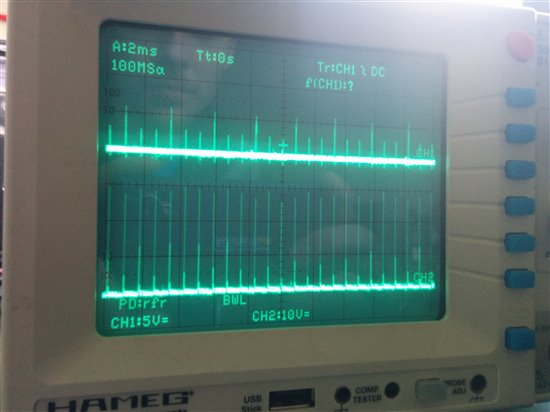

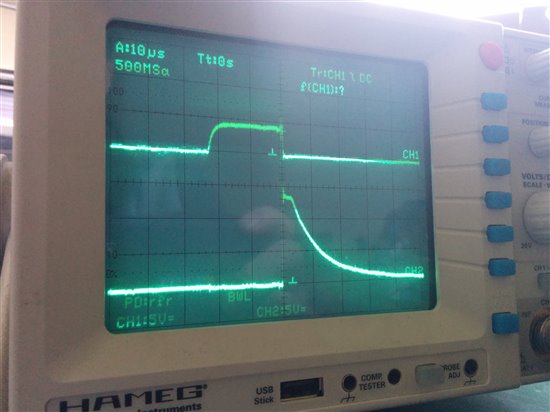

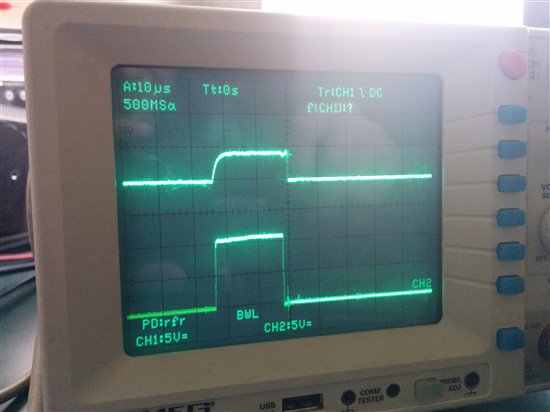

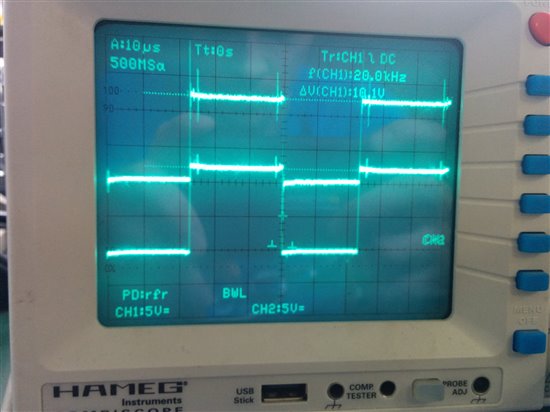

Now, the issue is: when i start the commutation, the fault pin is triggerd in a seemingly random pattern. It is not latched, 'OCTW is not triggered and in the SPI-registers I can't find any faultreports. Unfortunately this happens also, if the DutyCycle is down to 0 and no matter if any Motor is connected or not.

edit: Almost forgot to mention: DVDD looks just fine.

First thing I checked was the connections and solderjoints, but they were fine. I tried different PWM-Frequenzes but it only got worse at multiples of 4880Hz. C_CP is about 15mm away from the DRV and on the opposite layer, Could it be that there is an inductance caused by the vias that causes the troubles? I'm running out of Ideas.

Please let me know, if you have any Idea how to fix this. I'd be happy send you my layoutfiles if thats of any help.

Best Regards,

Tobias Müllensiefen