Part Number: DRV8432

Quote from datasheet:

“The DRV84x2 contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overcurrent, overtemperature, and undervoltage. The DRV84x2 responds to a fault by immediately setting the half bridge outputs in a high-impedance (Hi-Z) state and asserting the FAULT pin low. In situations other than overcurrent or overtemperature, the device automatically recovers when the fault condition has been removed or the gate supply voltage has increased.”

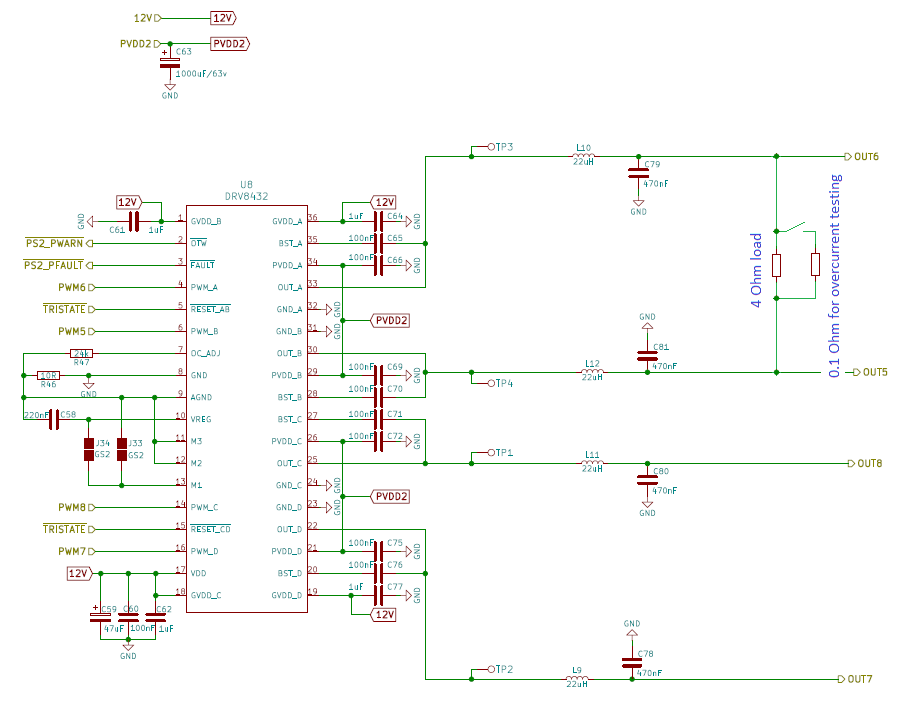

When I send input PWM and short the load with 0.1Ω I can see that the current limiting works. When the 0.1Ω is connected parallel to the load for short time, the ~FAULT pin remains high. When 0.1Ω is connected parallel to the load for longer time, say 0.1-0.5sec ~FAULT pin changes state to low, but DRV8432 remains fully operational - when I remove 0.1Ω undistorted signal appears on the output. However ~FAULT pin remains low until reset. What is the logic behind ~ FAULT pin operation in CBC current limiting mode? Thank you